# Design Of Low Power Voltage Doubler Circuit For Power Harvesting Applications

N.Ameer Suhail<sup>1</sup>, S.Anusooya<sup>2</sup>

<sup>1</sup>Dept of M.Tech(VLSI & Embedded Systems) <sup>2</sup>Assistant Professor,Dept of ECE <sup>1, 2</sup>B.S.Abdur Rahman Crescent institute of science and technology, Vandalur, Chennai

Abstract- Implementation of power efficient and reliable device requires high end batteries and sustainable energy's. The major drawback of this sustainable energy is that, the low voltage generation makes it difficult to drive the device. To overcome this side-effect we make use of voltage doubler (DC-DC converter) circuit to convert low voltage to high voltage where it can able to drive the circuit and used in energy/power harvesting applications. Considering the ideal voltage doubler circuit in cmos circuit design and analyse the performance in terms of power and delay. Instead of using capacitor in the ideal voltage doubler circuit we make use of MOS capacitor which has less delay and less power dissipation than the ideal voltage doubler circuit. Later we modified the cmos inverter in the ideal voltage doubler circuit using FinFet inverter where the power dissipation of the FinFet inverter based voltage doubler (in uW) reduces futhermore than the ideal voltage doubler and the MOS capacitance voltage doubler (in mW) which can be utilized in the energy harvesting application.

### I. INTRODUCTION

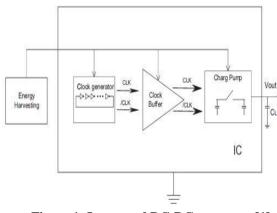

In the modern era progress in the innovation of wired gadgets and small scale remote wearable frameworks is important to build up a low power consuming frameworks. To do so we require high end petroleum products, batteries and supportable vitality. Because of rising energy cost and decrease of assets we move to very good quality batteries, though in batteries it requires high supply to work the gadgets which makes the gadget more power subordinate. So we utilize feasible energy sources for example, piezoelectric, [1].The and photovoltaic thermoelectric principle disadvantage of utilizing this manageable vitality is their low voltage generation, which is the fundamental pleat of utilizing this gadgets. Thus, in the ongoing year, part of research has been occurred to create a proficient DC-DC converter, which is equipped for changing over low voltage level to higher voltage level with high productivity and low power utilization. Self-one-sided exchanging controller is utilized for efficient DC-DC converters. Considering the fundamental block of DC-DC boost converteras described in figure 1[1]

A completely coordinated capacitive DC-DC voltage converter which essentially comprises of three area clock generator, clock buffer and charge pump.

The clock generator is utilized produce the necessary clock sign and equivalent timing of the voltage doubler circuitry for minimum DC input voltage. Clock buffer are used for high drive and to produce exact square wave. The charge pump of exchanged capacitor circuit convert low DC input voltage to high DC yield voltage. The charge siphons are various sorts and can incorporate different advance or multistage structures. These three area in the incorporated circuit are provided by the TEG energy harvester utilized in biomedical applications and furthermore can be utilized in low power applications.

### **1.2 THE CHARGE PUMP**

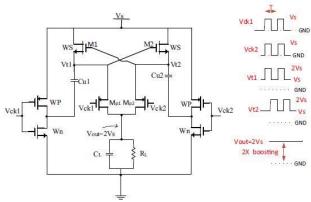

A circuit of single stage voltage doubler is considered in the figure 2[12] .where as vck1 and vck2 are two inputs given to the circuit. Process of the circuit is given in two steps

Figure 2: Voltage Doubler Circuit [12]

1) When clock1=0 and clock2=1:

Wp turns ON and Wn turns OFF.M2 turns ON where vt2= VS. Due to this the capacitor is charged to VS [cu2=VS].Because of the previous clock input the capacitor cu1 is charged to VS, so the output of the circuit becomes 2 VS [Vout=2VS]

2) When clock1=1 and clock2=0:

Wp turns ON and Wn turns OFF.M1 turns ON where vt1=VS. Due to this the capacitor is charged to VS [cu1=VS].Because of the previous clock input the capacitor cu2 is charged to VS, so the output of the circuit becomes 2 VS [Vout=2VS]

### **II. VOLTAGE DOUBLER USING MOS CAPACITOR**

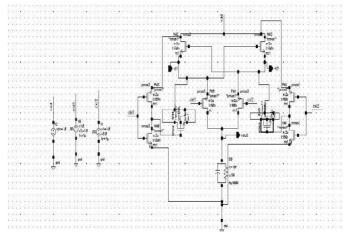

In order to reduce the power consumption and delay in the circuit, we make use of the MOS capacitor instead of normal capacitor in the ideal voltage doubler circuit. The main advantage is that it reduces the capacitor effect in the circuit. By using a MOS capacitor it reduces the complexity of the circuit during the fabrication process. MOS capacitor is nothing but metal oxide semiconductor capacitor where it has three terminals gate, drain and source. By shorting source and drain we make it as a MOS capacitor. The output of the circuit Vout is 3.045V.

Figure 3: MOS Capacitor Voltage Doubler

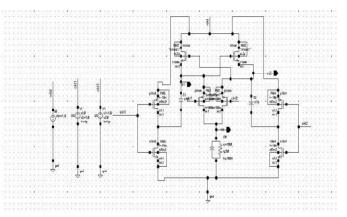

## 2.1 IDEAL VOLTAGE DOUBLER WITH FINFETINVERTER

So as to lessen the power utilization in the circuit, we utilize FINFET inverter rather than typical inverter in the perfect voltage-doubler circuit. The main advantage is to reduce the second-order effect in the circuit. By using FINFET inverter it reduces the complexity of the circuit during the fabrication process and also consumes less area. FINFET is nothing but fin field-effect transistor, here the directing Channel is wrapped by a dainty silicon "fin" which frames the gate of the gadget. The output of the voltage doubler with FINFET inverter Vout is 3.32V.

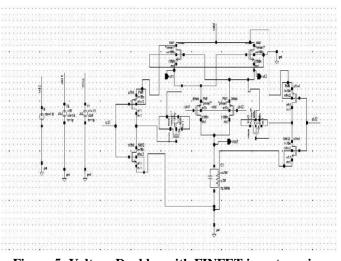

Figure 4: Voltage Doubler with FINFET inverter

## 2.2 VOLATGE DOUBLER CIRCUIT WITH FINFET INVERTER USING MOS CAPACITANCE

So as to lessen the power utilization and delay in the circuit, we make use of the MOS capacitor instead of a normal capacitor in the ideal voltage doubler circuit with FINFET inverter. The main advantage is that it reduces the capacitor effect in the circuit. By using a MOS capacitor it reduces the complexity of the circuit during the fabrication process. MOS capacitor is nothing but metal oxide semiconductor capacitor where it has three terminals gate, drain and source. By shorting source and drain we make it as an MOS capacitor. Output of the circuit Vout is 3.3V

Figure 5: Voltage Doubler with FINFET inverter using MOS Capacitance

### **III. RESULTS**

doubler

capacitance

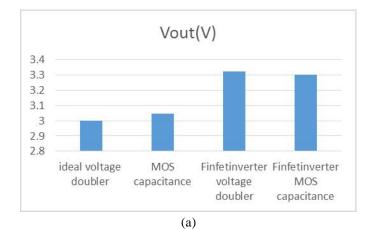

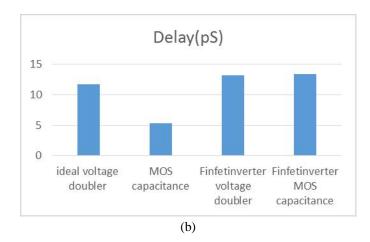

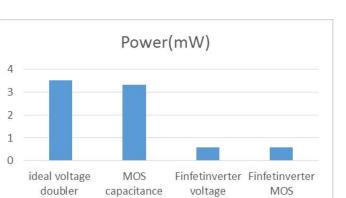

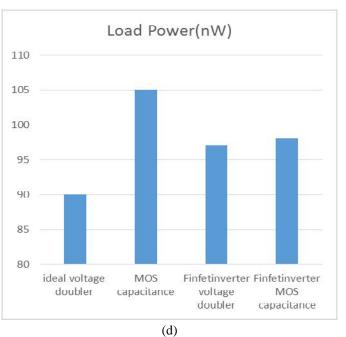

Figure 6: Comparison of four circuits: (a) output voltage, (b) delay, (c) power dissipation, (d) load Power

### **IV. CONCLUSION**

This paper presents a low-power, fully integrated DC-DC converter for energy harvesting application based on different voltage doubler structure. Initially capacitor in the ideal voltage doubler is replaced by the MOS capacitance which improves the performance of the circuit in terms of delay 6.113 X E-12 seconds and power dissipation is 3.588mW and load power 85.01nW when compared to the ideal voltage doubler circuit. Also, the cmos inverter circuit at the input stage is modified with the FINFET inverter to further improve the performance of the circuit. Whereas the power dissipation reduces to 570uW for MOS capacitance voltage doubler with FINFET inverter circuits. Load power of the MOS capacitance voltage doubler circuits. Load power of the MOS capacitance voltage doubler with FINFET inverter circuit set of the is less when compared to the other voltage doubler with FINFET inverter circuit is 96nW which is less when compared to ideal voltage

### ISSN [ONLINE]: 2395-1052

doubler circuit, MOS capacitance voltage doubler and voltage doubler using FinFet inverter.

#### REFERENCES

- Elham Kordetoodeshki, Alireza Hassanzadeh. An ultralow power, low voltage DC-DC converter circuit for energy harvesting applications. International Journal of Electronics and Communications (AEÜ). Elsevier. 2019

- [2] Maciel WH, Augusto J, Carvalho R, Tofoli FL. A unified modeling approach for DC-DC converters based on the three-state switching cell. Int J Electron Comm (AEÜ) 2018; 2.

- [3] Le HP, Sanders SR, Alon E. Design techniques for fully integrated switched capacitor dc-dc converters. IEEE J Solid-State Circuits 2011; 46(9):2120–31.

- [4] Santa T, Auer M, Sandner C, Lindholm C. Switched capacitor dc-dc converter in 65nm CMOS technology with a peak efficiency of 97%. IEEE Int Symp Circuits and Syst (ISCAS) 2011:1351–4.

- [5] Yi H, Yin J, Mak P, Martins RP. A 0.032-mm2 0.15-V 3-Stage charge-pump scheme using a differential bootstrapped ring-VCO for energy-harvesting applications. IEEE Trans Circuits Syst 2018; 65(2):146– 50.

- [6] Chen Z, Law MK, Mak P, Martins RP. A single-chip solar energy harvesting IC using integrated photodiodes for biomedical implant applications. IEEE Trans Biomed Circuits Syst 2017; 11(1):44–53.

- [7] Kim J, Mok PKT, Kim C. A 0.15V-input energyharvesting charge pump with switching body biasing and adaptive dead-time for efficiency improvement.IEEE J. Solid-State Circ 2015;50(2):414–25.

- [8] Wang X, Zhang Y, Lu C, Mao Z. Power efficient SRAM design with integrated bit line charge pump. Int J Electron Comm (AEÜ) 2016:8.

- [9] Cheng HC, Lin MY, Chen PH. A tri-mode fullyintegrated capacitive voltage multiplier for photovoltaic energy harvesting. In: IEEE Wireless Power trans.Conf., 2017, p. 4.

- [10][10]Kim J, Mok PKT, Kim C, Khai Y. A low-voltage high-efficiency voltage doubler for thermoelectric energy harvesting. IEEE Elec. Dev. Solid-state Circ. (EDSSC) Conf.; 2013.p 1-3.

- [11] Intaschi L, Bruschi P, Iannaccone G. A 220-mV input, 8.6 step-up voltage conversion ratio, 10.45-IW output power, fully integrated switched-capacitor converter for energy harvesting. In: IEEE Cust. Int. Circ. Conf. (CICC); 2017.

- [12] Liu X, Sinencio ES. An 86% efficiency 12IW selfsustaining PV energy harvesting system with hysteresis regulation and time-domain MPPT for IoT smart nodes. IEEE J Solid-State Circuits 2015; 50(6):1424–37.

- [13] Liu X, Sinencio ES. A highly efficient ultralow photovoltaic power harvesting system with MPPT for internet of things smart nodes. IEEE Trans Very Large Scale Intgr (VLSI) Syst 2015; 23(12):3065–75.

- [14] Teichmann P. Adiabatic logic: future trend and system level perspective. Dordrecht: Springer; 2012.

- [15] Van Breussegem T, Steyaert M. CMOS integrated capacitive DC-DC Converters. New York, NY, USA: Springer-Verlag; 2013.

- [16] Lee W, Wang Y, Cui T, Nazarian S, Pedram M. Dynamic thermal management for FinFET-based circuits exploiting the temperature effect inversion phenomenon. In: IEEE Low Power Elec Design (ISLPED); 2014.

- [17] Shin D, Chung SW, Chung EY, Chang N. Energy-optimal dynamic thermal management: computation and cooling power co-optimization. IEEE Trans on Indus Inform 2010; 6(3).

- [18] Skoplaki E, Palyvos JA. On the temperature dependence of photovoltaic module electrical performance: a review of efficiency/power correlations Elsevier. Sol Energy 2009; 83(5):614–24.

- [19] Kordetoodeshki E, Hassanzadeh A. Design of low voltage low power DC-DC converters using adiabatic technique. J Cir, Syst Comput 2018; 27(6):20.

- [20] Jung W, Oh S, Bang S, Lee Y, Foo Z, Kim G, et al. An ultra-low power fully integrated energy harvester based on self oscillating switched-capacitor voltage doubler. IEEE J Solid-State Circuits 2014; 49(12):2800–11.

- [21] Kennedy S, Yuce MR, Redout'e JM. A low-EMI fully integrated switched capacitor.IEEE Trans Electromag Compat 2018; 60(1).