# Design and Implementation of FMO/Manchester Encoding By Using SOLS Technique

K.Logeswari<sup>1</sup>, P.Sridevi<sup>2</sup>, P.Krishnakumar<sup>3</sup>, B.Gowri Sankaran<sup>4</sup>

<sup>1</sup>Dept of Electronics and communication Engineering <sup>2, 4</sup>Associate Professor, Dept of Electronics and communication Engineering <sup>3</sup>Assistant Professor, Dept of Electronics and communication Engineering <sup>1, 2, 3, 4</sup>Sri Ramanujar Engineering College

Sri Ramanujar Engineering College

Abstract- The dedicated short-range communication (DSRC) is an emerging technique to push the intelligent transportation system into our daily life. The DSRC standards generally adopt FMO/Manchester/Miller codes to reach Dc-balance, enhancing the signal reliability. Nevertheless, the codingdiversity between the FMO, Manchester, Miller codes seriously limits the potential to design a fully reused VLSI architecture for both. In this project, the similarity oriented logic simplification (SOLS) techniques is proposed to overcome this limitation and also used to improve the hardware utilization rate. By using two code power, delay and area can be reduced. The proposed architecture will have less delay, area as compared to existing architecture. In this paper the architecture analyzed to reduced the num of components. Using SOLS technique to reduced the area, delay and power.

*Keywords*- FMO, Manchester, Miller and SOLS technique.

# I. INTRODUCTION

The dedicated short range communication is a protocol for one or two way medium range communication. The DSRC can be briefly classified into two categories: Automobile-to-automobile and automobile-to-roadside. In automobile-to-automobile, the DSRC enables the message sending and broadcasting among automobile. The automobile-to-roadside focuses on the intelligent transportation service, such as electronic toll collection (ETC).

Antenna Transmission Baseband DSRC RF Front-End Processing Information Microprocessor Antenna DSRC Baseband ((q)) **RF Front-End** Information Processing Receiving

Fig 1. DSRC Transceiver.

The DSRC architecture having the transceiver. The transceiver having the baseband processing, RF front end and microprocessor. The microprocessor is used to transfer the instruction to the baseband processing and RF front end. The RF front end is used to transmit and receive the wireless signals using the antenna. The baseband processing is responsible for modulation, error correction, encoding and synchronization. The Similarity Oriented Logic Simplification having the two methods: Area Compact Retiming and Balance Logic Operation Sharing. The area compact retiming used to reduce the transistor counts and the balance logic operation sharing used to combine FMO and Manchester encoding.

# **II. FMO ENCODING**

Flexible Macroblock Ordering or FMO is one of several error resilience tools defined in the Baseline profile of the H.264/MPEG - 4 AVC video compression standards. This way, FMO allows more flexibly deciding what slice macroblocks belong to, in order to spread out errors and keep errors in one part of the frame from compromising another part of the frame. Certain advanced encoding techniques can simulate some of FMO's benefits. In H.264/AVC, P (predicted) and B (bipredicted) frames may contain I (intra) blocks, which store independent picture. Rather than create a slice in order to periodically refresh entirely with I or IDR frames I-blocks can be sent in any desired pattern while predicted blocks make up the rest of the picture.

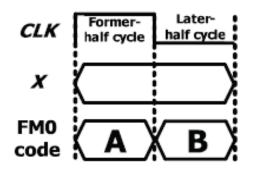

Fig 2. Code Word Structure of FMO

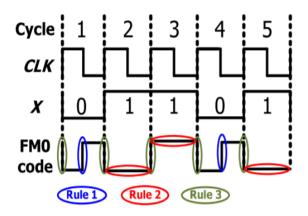

The coding principles of FMO is listed as the following three rules.

- 1) If X is the logic-0, the FMO code must exhibit a transition between A and *B*.

- 2) If X is the logic-1, no transition is allowed between A and B.

- 3) The transition is allocated among each FMO code no matter what the X.

Fig 3. FMO Encoding

### **III. SOLS TECHNIQUE**

The SOLS technique which is used to eliminates the coding diversity between Manchester and FMO encoding. The SOLS technique is eliminate the limitation on hardware utilization by two important techniques. Using compact retiming the number of transistor is reduced as 22. Using logic operation sharing, HUR was achieved as 100%. The maximum operation frequency of both Manchester and FMO encoding are 2GHz, 900MHz. The power consumption of Manchester and FMO encodings are 1.58mW, 1.14mW. The intention of SOLS scheme is to design a fully salvaged VLSI architecture for Manchester and FMO encodings. The SOLS technique is divided into two categories:

1) Area Compact Retiming.

2) Balance logic operation sharing.

### IV. MILLER AND FMO ENCODING

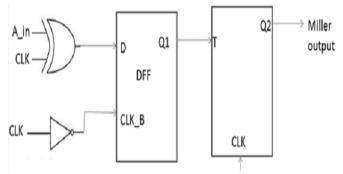

An Miller encoding is also known as delay encoding. It can be used for higher operating frequency and it is similar to Manchester encoding except that the transition occurs in the middle of an interval when the bit is 1. While using the Miller delay, noise interference can be reduced. The block diagram has a d flip flop, t flip flop, NOT gate, and XOR gate. Where the input is A in and CLK, then the output is a Miller output. For example, if the input is 0 and the clock, given the XOR operation has done that, is A\_in CLK, therefore 0 plus a positive edge clock produces the output as 0. Given to d flip flop, the clock has inverted, and after that output is given to t flip flop it inputs as d flip flop output, which is 0. Then the TFF is toggle FF, which produces the Miller output as 1.

Fig 4. Block diagram for Miller encoder

The four states available are 00, 01, 10, 11. There is also RST. Transition is obtained based on 1 and 0. In the initial state, reset is 1. Then the next state will be 00, and after this reset it will always be 0. When the input is 0, and the current state is 00, the next state is 10. If the input is 1, and the current state is 00, the next state is 01. If the input is 0, and the current state is 01, the next state is 10. And if the input is 1, and the current state is 01, the next state is 01. If the input is 0, and the current state is 10, the next state is 01. If the input is 0, and the current state is 10, the next state will be 11. If the input is 1, and the current state is 11, the next state will be 01. And if the input is 1, and the current state is 11, the next state is 10.

#### Table 1. State machine diagram for miller encoder

| Reset | Input | Current State | Next State |  |

|-------|-------|---------------|------------|--|

| 1     |       | -             | 00         |  |

| 0     | 0     | 00            | 10         |  |

| 0     | 1     | 00            | 01         |  |

| 0     | 0     | 01            | 10         |  |

| 0     | 1     | 01            | 01         |  |

| 0     | 0     | 10            | 11         |  |

| 0     | 1     | 10            | 00         |  |

| 0     | 0     | 11            | 01         |  |

| 0     | 1     | 11            | 10         |  |

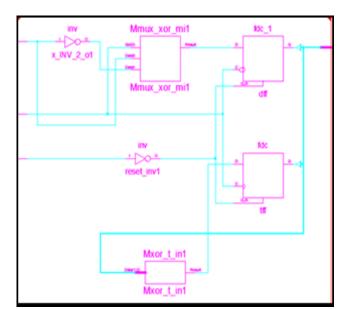

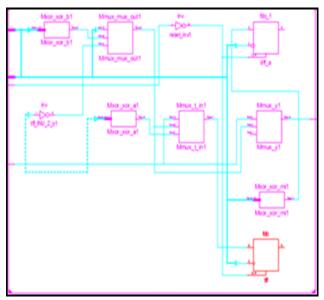

Fig 5. Illustration of area-compact retiming on Miller encoding architecture

To replace the Manchester encoder by miller encoder to the figure 8. And to rearrange and remove the some element based on the sharing the logic or component. After this operation to get the prepare balanced logic-operation sharing circuit.

Fig 6. Architecture of FM0 and Miller encodings using SOLS technique

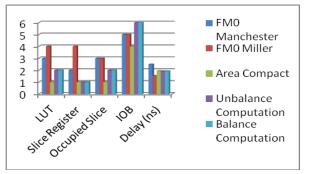

**Table 2. Comparison Table**

|              | FM0<br>Man | FM0<br>Miller | Area<br>Compact | UBC   | BC    |

|--------------|------------|---------------|-----------------|-------|-------|

| LUT          | 3          | 4             | 1               | 2     | 2     |

| Slice<br>Reg | 2          | 4             | 1               | 1     | 1     |

| OC           | 3          | 3             | 1               | 2     | 2     |

| IOB          | 5          | 5             | 4               | 6     | 6     |

| Delay        | 2.498      | 1.535         | 1.943           | 1.914 | 1.914 |

| Power        | 23         | 23            | 23              | 23    | 23    |

**Chart 1. Simulation Result**

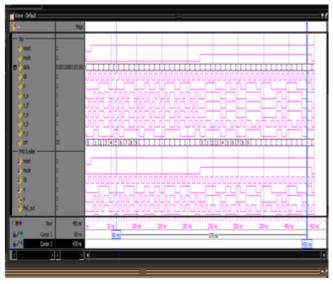

Fig 7. Simulation of Proposed Encoder

### **VI. CONCLUSION**

In this paper, we have designed the architecture of a New Proposed Encoder which integrates the FMO, Manchester and Miller Encoding using SOLS techniques. In the first part we have integrated the FMO/Manchester encoding applied SOLS technique is proposed to overcome this limitation and also used to improve the hardware utilization rate. By using two code power, delay and area can be reduced. The proposed architecture will have less delay, area as compared to existing architecture. In this paper the architecture analyzed to reduced the number of components. Using SOLS technique to reduced the area, delay and power.

#### REFERENCES

- [1] Yu-Hsuan Lee, Member, IEEE, and Cheng-Wei Pan, Fully Reused VLSI Architecture of FMO/Manchester Encoding Using SOLS Technique for DSRC Applications, IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 23, NO. 1, JANUARY 2015

- [2] F. Ahmed-Zaid, F. Bai, S. Bai, C. Basnayake, B. Bellur,S.Brovold,et al., "Vehicle safety communications—Applications (VSC-A) final report," U.S. Dept. Trans., Nat. Highway Traffic Safety Admin., Washington, DC, USA, Rep. DOT HS 810 591, Sep. 2011.

- [3] J. B. Kenney, "Dedicated short-range communications (DSRC) standards in the United States," Proc. IEEE, vol. 99, no. 7, pp. 1162–1182,Jul. 2011.

- [4] J. Daniel, V. Taliwal, A. Meier, W. Holfelder, and R. Herrtwich, "Design of 5.9 GHz DSRC-based vehicular safety communication,"IEEE Wireless Commun. Mag., vol. 13, no. 5, pp. 36–43, Oct. 2006.

- [5] P.Benabes, A. Gauthier, and J. Oksman, "A Manchester code generator running at 1 GHz," in Proc. IEEE, Int. Conf. Electron., Circuits Syst., vol. 3. Dec. 2003, pp. 1156–1159.

- [6] A. Karagounis, A. Polyzos, B. Kotsos, and N. Assimakis, "A 90nm Manchester code generator with CMOS switches running at 2.4 GHz and 5 GHz," in Proc. 16th Int. Conf. Syst., Signals Image Process., Jun. 2009, pp. 1– 4.

- [7] Y.-C. Hung, M.-M. Kuo, C.-K. Tung, and S.-H. Shieh, "High-speed CMOS chip design for Manchester and Miller encoder," in Proc. Intell. Inf. Hiding Multimedia Signal Process., Sep. 2009, pp. 538–541.

- [8] M. A. Khan, M. Sharma, and P. R. Brahmanandha, "FSM based Manchester encoder for UHF RFID tag emulator," in Proc. Int. Conf. Comput., Commun. Netw., Dec. 2008, pp.16.

- [9] M. A. Khan, M. Sharma, and P. R. Brahmanandha, "FSM based FMO and Miller encoder for UHF RFID tag emulator," in Proc. IEEE Adv. Comput. Conf., Mar. 2009, pp. 1317–1322.

- [10] J.-H. Deng, F.-C. Hsiao, and Y.-H. Lin, "Top down design of joint MODEM and CODEC detection schemes for DSRC coded-FSK systems over high mobility fading channels," in Proc. Adv. Commun. Technol. Jan. 2013, pp. 98–103.

- [11] I.-M. Liu, T.-H. Liu, H. Zhou, and A. Aziz, "Simultaneous PTL buffer insertion and sizing for

minimizing Elmore delay," in Proc. Int. Workshop Logic Synth., May 1998, pp. 162-168.

- [12] H. Zhou and A. Aziz, "Buffer minimization in pass transistor logic" IEEE Trans comput, Aided Des, Integr. Circuits Syst., vol 20, no.5 pp. 693-697, May 2001.

- [13] N.H.E. Weste and K. Eshraghian, Principles of CMOS VLSI Design: A System Perspective, 2<sup>nd</sup> ed., Upper Saddle River, NJ, USA: Pearson Educ. Ltd., 1993, pp. 98-103