# Study of Designing of N-Bit Linear Feedback Shift Register For Communication

Naincy Soni<sup>1</sup>, Dr. Nidhi Tiwari<sup>2</sup> <sup>1, 2</sup> Dept of Electronics & Communication <sup>1, 2</sup> SAGE University Indore

Abstract- This paper has examined the idea of PN sequence and design of linear feedback shift register as applicable to spread spectrum code division multiple access technique. Maximum length sequence arrangements were presented, and utilized as a prologue to some difficult strategies for PN code generation with the assistance of LFSR. In linear feedback shift register, the feedback is used to modification on every clock cycle. In this paper we have studied the implementation n-bit LFSR, which can be used in communication. Different parameters are discussed.

*Keywords*- Shift Registers, LFSR, PN Sequence, CDMA, and Communication.

# I. INTRODUCTION

Considerable interest has developed during the past two decades in the binary feedback shift registers. These devices are capable of generating cyclic sequences possessing statistical properties which closely approximate those of binary random noise. Such, apparently random, but deterministic, sequences may be used, therefore, in place of this noise) and the results which are thus obtained are much more accurate than those obtained using binary noise. The ease and simplicity in generating and processing the sequences are further responsible for this development.

The arena of mobile communication is presently developing at very uncommon rate. This development provoked to a limited extent by the increasing rate, broadband communication, has prompted the requirements for high determination, broadband mobile measurement hardware. The wireless communication structure is one of most significant method in the entire existence of media transmission which has enhanced human development and mankind by uniting business and network. A pseudo noise sequence (PN sequence) is assigned to each user in the spread spectrum code division multiple access schemes for the purpose of grouping and dispreading. In this way PN sequence is viewed as the core of CDMA/SS-CDMA systems. The maximal length pseudo noise sequence is best depicted sequence whose length is same with its period. Linear feedback shift register i.e. LFSR is used to generate multiple PN sequence. In this shift register feedback is provided by essential feedback taps. By VLSI technology, the implementation of LFSR circuit can be used in less delayed communication system designs.

The objective of this work is to evaluation of n-bit Linear Feedback Shift Register using memory element. Also designing the LFSR for the application of CDMA, where PN sequence is multiply with input message to add the security while transmitting the codeword into wide range of frequency. Bascially CDMA works in the frequency range of 900 MHz to 1.9 GHz so the objective of this work is to design and implement LFSR for this frequency range.

## **II. LITERATURE REVIEW**

**Mishra Shivshankar et al. [1],** in this paper author suggested and implemented the configurable linear feedback shift register. They assess the results in terms of logic, memory and speed requirements using Xilinx ISE 9.2i tool. Their targeted device for implementation is Vertex-4 FPGA board. The implemented 8 bit and 16 bit CLFSR completes the output sequence cycle in 51000 ns and 13107000 ns. Author also suggested various applications of CLFSR like PN sequence generator, Gold code generator and CRC generator.

**R** Saraswathi et al. [2], in this paper author described the design and implementation of linear feedback shift register (LFSR) for low power test pattern generator. They modified the existing design of linear feedback shift register by utilizing transition controllers. Their simulation and results are achieved through Altera Quartus 16.0. They compared their results for power consumption and Number of test pattern generated.

**Tejas Thubrikar et al. [3],** in this research manuscript author designed and implemented 32 bit low power test pattern generator using linear feedback shift register. Their whole design is implemented in Xilinx ISE 13.1i using VHDL language. By using extra combinational circuit in the existing design of LSFR they achieved 50% reduction in power consumption. Also they attained less number of slice register used and less number of LUT's.

**Roshni Jamgade et al. [4],** in this paper the author suggested new method for designing of linear feedback shift register. They used vedic multiplication which is the oldest method for multiplication using vedic formulas. Author suggested the application of linear feedback shift register for generation of PN sequence which is used in CDMA for multiplication with original sequence of message to add the security in transmission over a wide frequency. Area and delay analysis is done in this existing work.

**Debarshi Datta et al. [5],** this paper suggested the design and implementation of multibit linear feedback shift register to generate PN sequence codes which are very useful in CDMA. They designed the circuit using pseudo random number generator (PRNG) in HDL language. Their targeted device for implementation is Vertex-4 FPGA board for implementing 8 bit, 16 bit and 32 bit LFSR. They compared the results for various parameters like number of slice registers, occupied slices, and number of input output blocks, delay and power consumed.

Table 1: Comparison of various parameters of some research papers

| researen papers |                           |          |                           |                                       |               |                   |

|-----------------|---------------------------|----------|---------------------------|---------------------------------------|---------------|-------------------|

| S.<br>N<br>o    | Name of<br>the<br>Author  | Ye<br>ar | No of<br>Bits             | Para<br>mete<br>r                     | FPGA<br>Used  | Tool<br>Used      |

| 1               | Mishra<br>Shivshank<br>ar | 201<br>6 | 8/16                      | Timin<br>g                            | Vertex<br>4   | Xilinx            |

| 2               | R.<br>Saraswathi          | 201<br>7 | 8                         | Powe<br>r                             |               | Altera<br>Quartis |

| 3               | Tejas<br>Thubrikar        | 201<br>7 | 8                         | Powe<br>f                             |               | Xilinx            |

| 4               | Roshni<br>Jamgade         | 201<br>5 | 8                         | Powe<br>f                             | Virtex<br>7   | Xilinx            |

| 5               | Debarshi<br>Dutta         | 201<br>7 | 8/16                      | Delay                                 | Sparta<br>n 6 | Xilinx            |

| 6               | Proposed                  | 202<br>0 | 4, 8,<br>16, 32<br>and 64 | Powe<br>r/Del<br>ay/Fr<br>eque<br>ncy | Artix<br>7    | Xilinx            |

Based on the above literature review, contribution in this field is proposed as:

- 1. To study and to analysis the performances of LFSR for generating PN Sequence with application in CDMA.

- 2. Decreasing the utilization of number of slices.

- 3. Decreasing the output delay time by optimizing the levels.

- 4. Reducing the power dissipation.

- 5. Taking the schematic up to the layout.

6. Compare the parameters with existing methods.

#### **III. METHODOLOGY**

On the There are many applications of linear feedback shift registers, and it is commonly used in mobile communications where pseudo random sequence is required. These are the basic blocks of many circuits like PN sequence generator, gold code producer which is used in spread spectrum code division multiple access techniques. Linear feedback shift registers are extensively used for binary counters to generate random number sequences. Maximum time the generated sequence is pseudorandom in nature. These patterns may repeat over period, as longer the shift registers. This repetition is depends on the number of taps present in the registers. For large pattern generation, the size of hardware may be increased. Conservatively, for the older architectures of FPGA, flip flops were used. LFSR sequences are generated through  $2^{N} - 1$  state, where N is the number of flip-flops/taps in the LFSR. After every edge of clock, the data of flip flop is shifted right. The feedback path is provided from previous register to the left most register through an XOR or XNOR gate. Value of 0's is illegal for XOR feedback path similarly value of 1's is illegal for XNOR feedback path. These illegal states may cause the shift register to present in its present state [13].

A 4-bit LFSR sequences generated through  $(2^4 - 1)$  is having 15 states (the state 1111 is in the illegal state) from the feedback taps 4 and 3. At the same time, a 4 bit binary counter may generate the sequence by  $2^4$  i.e. 16 states without any illegal stages. Still linear feedback shift register are faster than normal counter because they don't have carry signal. Linear feedback shift register are the substitute of normal binary counters in perilous applications where the counted sequence is not that much important. Linear feedback shift register are also used as pseudo random sequence generators. These are the basic blocks of many circuits like PN sequence generator, gold code producer which is used in spread spectrum code division multiple access techniques. The tap sequence is responsible to affect the bits positions of next bits.

The n bit LFSR whose maximum feedback polynomial is represented as follows:

Table 2: Generator polynomial for LFSR

| Number of | Generator                                                             |

|-----------|-----------------------------------------------------------------------|

| Bits      | Polynomial                                                            |

| 4         | X_+X_+]                                                               |

| 8         | X*+X+X+X+X+1                                                          |

| 16        | x <sup>10</sup> +x <sup>15</sup> +x <sup>14</sup> +x <sup>0</sup> +1  |

| 32        | x**+x**+x*+x+1                                                        |

| 64        | X <sub>2c</sub> +X <sub>2c</sub> +X <sub>2c</sub> +X <sub>2c</sub> +1 |

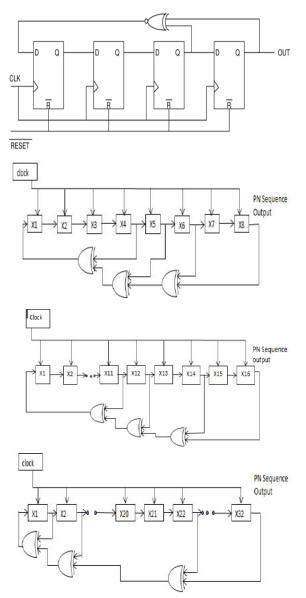

The general block diagram for 4, 8, 16 and 32 bit is shown as below:

Figure 1: General block diagram of LFSR

#### **IV. EXPECTED SIMULATION**

All the experiment analysis will be done by 14.1i in Vertex device family. The significant benefit of this software is low-memory with high-speed analysis of any complex circuit. Simulation and synthesize of Linear Feedback Shift Register circuit may be improved by Xilinx design suit 14.1i Vertex device family series and device.

# **V. CONCLUSIONS**

In linear feed-back shift register incoming bit is linearly fed to its earlier state. Its initial value is known as seed. The operation performed by LFSR is deterministic, thus the pseudo sequence generated by shift register is purely determined by previous or current stage. The linear function of bit are XORing and reverse XORing, that's why it is a register where input bits are obsessed by XOR of few bits of the total register value. We have studied a LFSR which is used to generate PN sequence in various applications like Counters, CDMA, cryptography, test pattern generation and digital broadcasting etc.

## REFERENCES

- [1] Shivshankar Mishra, Ram Raksha Tripathi and Devendra Kr. Tripathi, "Implementation of Configurable Linear Feedback Shift Register in VHDL", International Conference on Emerging Trends in Electrical, Electronics and Sustainable Energy Systems (ICETEESES–16).

- [2] R. Saraswathi, R.Manikandan, "Design of LFSR for low Power Test Pattern Generator", IEEE NetACT 2017

- [3] Tejas Thubrikar et. al. "Design and Implementation of Low Power Test Pattern Generator Using Low Transitions LFSR" International Conference on Communication and Signal Processing, IEEE 2017

- [4] Roshni Jamgade et. al. "Design and Implementation of PN Sequence Generator using Vedic Multiplication" International Conference on Advances in Computer Engineering and Applications (ICACEA) IEEE 2015

- [5] Debarshi Dutta et. al. "Design and Implementation of Multibit LFSR on FPGA to Generate Pseudorandom Sequence Number" Devices for Integrated Circuit (DevIC), IEEE 2017

- [6] Katti, R.S. Srinivasan, S.K., "Efficient hardware implementation of a new pseudo-random bit sequence generator," IEEE International Symposium on Circuits and Systems, 2009.

- [7] K. Panda Amit, P. Rajput, B Shukla, "Design of Multi Bit LFSR PNRG and Performance comparison on FPGA using VHDL," International Journal of Advances in Engineering & Technology (IJAET), Mar 2012, Vol. 3, Issue 1, pp. 566-571.

- [8] Sewak K, Rajput P, Panda Amit K, "FPGA Implementation of 16 bit BBS and LFSR PN Sequence Generator: A Comparative Study," In Proc. of the IEEE Student Conference on Electrical, Electronics and Computer Sciences 2012, 1-2 Mar 2012, NIT Bhopal, India.

- [9] A. K. Panda, P. Rajput and B. Shukla, "FPGA Implementation of 8, 16 and 32 Bit LFSR with Maximum Length Feedback Polynomial using VHDL," IEEE Int. Conference on Communication Systems and Network Technologies, DOI 10.1109, 2012.

- [10] S. Hathwalia and M. Yadav, "Design and Analysis of a 32 Bit Linear Feedback Shift Register Using VHDL", Int.

Journal of Engineering Research and Applications, ISSN: 2248-9622, Vol. 4, Issue 6(Version 6), pp.99-102, June 2014.

[11] K. C. Sekhar and K. S. Raj, "An Efficient Pseudo Random Number Generator for Cryptographic Applications", Int. Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-4 Issue 1, October 2014