# A 250mv Sub-Threshold Operational Transconductance Amplifier

Vijay Solanki <sup>1</sup>, Ritu Chalotre <sup>2</sup> <sup>1, 2</sup> Dept of ECE <sup>1, 2</sup> SAGE University,Indore

Abstract- This paper show's the operational transconductance amplifier in which all the MOSFET are working in subthreshold region. With the help of this concept, gain of 72dB and 14.47kHz of unity gain frequency is achieved. This OTA is consuming less power as this OTA is working at 250mV supply and total current of 130nA. This OTA can be good candidate for low power circuit's, bio-medical applications.

*Keywords*- Sub-threshold, OTA, Gain, MOSFET, unity gain frequency and power.

## I. INTRODUCTION

An operational trans-conductance amplifier (OTA) is a voltage input, current output amplifier[1].

The input voltage Vin and the output current Io are related to each other by a constant of proportionality and the constant of proportionality is the trans-conductance "gm" of the amplifier.

Io=gm\*Vin

Where gm= trans-conductance of OTA Vin=differential input voltage

Operational trans-conductance amplifier(OTA) is the vital part of the most of application such as bio-medical field etc. Since this field needs to be operate at very low voltage and low power consumption, so the first requirement is low supply, secondly low operation current i.e. bias current. There are many parameter of an basic OTA such gain, CMRR[4] etc. Out of all the parameter, gain is the key parameter which should by high because all the bio-medical application require high gain. High gain means high amplification of input signal acquire by an OTA.

But the OTA used in the previous paper's[5] were consuming more power as they are working around 1.0V-1.8V supply and since all the transistor working in saturation region, all consume larger current.

So a alternative OTA is shown in this paper where all the transistor working in sub-threshold region with supply of 0.25V and the whole OTA is working at current of 130nA. This OTA is producing gain of 72db with UGB of 14kHz and bandwidth of 11 Hz.

## II. PROPOSED OTA

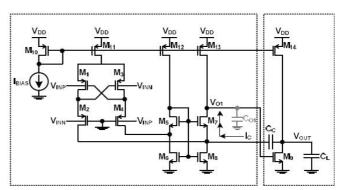

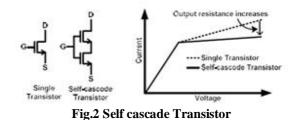

Fig. 1 shows the conventional Miller compensation bulkdriven input OTA [2]. It consists of two stage amplifiers. All transistors in the OTA operate in the weak inversion. all transistors in Fig. 1 are implemented with a self-cascode transistor in Fig. 2 to increase the DC-gain of the OTA. The self-cascode transistor is very effective method to increase the transistor output resistance by reducing the channel length modulation [5], [6].

To avoid the direct connection, the proposed OTA in Fig. 1 uses the indirect feedback compensation method [3]. This method has no direct connection between the first and second stage outputs.

Therefore, it changes the right-half-plane zero (RHZ) to the left-half-plane zero (LHZ), but it still has the Miller effect to increase CC for the frequency compensation.

Fig. 1 . Circuit Diagram of Proposed OTA

www.ijsart.com

## IJSART - Volume 5 Issue 4 – APRIL 2019

The transistor's are kept in sub-threshold region[2] except M1-M4 in which all the transistor works threshold region. The input transistor are bulk driven(M1-M4) i.e. the bulk is connected to a bias voltage that reduces the threshold voltage. So the OTA can work at low input voltage since the threshold voltage gets reduced.

# **III. SIMULATION RESULT**

The proposed OTA was implemented in a 32nm CMOS process. The transistor sizes in the OTA are given in Table I. All transistors are implemented with the self-cascode transistor having two same transistors as shown in Fig. 2. The biasing currents are 10nA in M1~M8 in the first stage, the bias current is 100nA in M9 in the second stage. All simulations are performed at 250mV supply-voltage (VDD) and the load capacitor (CL) is 50pF.

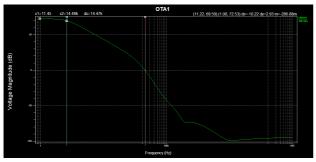

Fig. 3 shows the simulation results of the proposed OTA with CC=0.6pF. Table II shows the comparison results of the bulk-driven input OTAs. They have 72dB gain. They consume 1.94 nW at 250mV supply-voltage. The proposed OTA expends the bandwidth from 10Hz to 11.45Hz and the unit-gain frequency from 13kHz to 14.47kHz.

TABLE I. TRANSISTOR SIZES

| Transist                       | Size      | Transist        | Size                 |

|--------------------------------|-----------|-----------------|----------------------|

| or                             |           | or              |                      |

| M <sub>1</sub> -M <sub>4</sub> | 64um/0.2u | $M_{s}, M_{7}$  | 6.1um/63nm           |

|                                | m         |                 |                      |

| M <sub>6</sub> ,M <sub>8</sub> | 15um/0.2u | M10,M12-        | 40um/0.2um,15um/0.2u |

|                                | m         | M <sub>13</sub> | m                    |

| M <sub>11</sub>                | 80um/0.2u | $M_{14},M_9$    | 130um/100nm,16um/10  |

|                                | m         |                 | 0nm                  |

Fig. 3 Frequency response

| ~~~~~~              |          |           |

|---------------------|----------|-----------|

|                     | Previous | Proposed  |

|                     | OTA[4]   | OTA       |

| Process             | 65nm     | 32nm      |

| Supply-Voltage      | 0.8V     | 0.25 V    |

| DC gain             | 65db     | 72db      |

| Power               | 34nW     | 1.94nW    |

| Bandwidth           | -        | 11.45Hz   |

| Unit gain frequency | -        | 14.47 kHz |

## TABLE II. COMPARISON TABLE

#### **IV. CONCLUSION**

This paper proposes the 250mV supply-voltage 72dB-gain OTA with an enhanced bandwidth and a reduced compensation-capacitor. The proposed OTA was implemented using a 32nm CMOS process. It has a 72dB-gain and consumes 1.94nW at 250mV supply-voltage. Its unit-gain frequency is 14.47kHz.

## REFERENCES

- [1] Jamuna G and Siva S yellampalli, "Design and analysis of CMOS OTA for 180 nm technology," IJESPR, Vol.15,Issue 1,pp.1-6,July 2014.

- [2] L. H. C. Ferreira and S. R. Sonkusale, "A 60-dB Gain OTA Operating at 0.25-V Power Supply in 130-nm Digital CMOS Process," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 6, pp. 1609-1617, Jun. 2014.

- [3] R. J Baker, CMOS circuit design, layout, and simulation, 3rd ed. New Jersey, NJ, USA: Wiley-IEEE press, 2007.

- [4] Ramakant Gayakwad, "Op-Amps and Linear Integrated Circuits," Pearson,4<sup>th</sup> edition, May 2015.

- [5] A. Gerosa, A. Neviani, "Enhancing output voltage swing in low-voltage micro-power OTA using self-cascode," Electronics Letters, vol.39, no.8, pp. 638-639, Apr. 2003

- [6] K. J. Baek et al, "Analogue circuit design methodology using selfcascode structures," Electronics Letters, vol.49, no. 9, pp. 591-592, Jun.2013.