# **4-Bit Finfet Based Priority Encoder**

# Kalpna Gurjar<sup>1</sup>, Mr Shyam babu singh<sup>2</sup> ITM GOI

Abstract- Priority encoder converts multiple binary inputs into binary representation of the index of active input bit with the highest priority. It is used where more than one device want to access the system, it decides the priority of the device to be serve by the system. Priority encoders are used when multiple devices have to share common resources. Several researches are made on these encoders but found no research work on FinFET based Priority encoder. The FinFET device has gained very much attention on recent VLSI designs and FinFET is the substitute for bulk CMOS at nano-scale because of its high short channel effect immunity, scalability and lower leakage power consumption. In this paper, a 4 input-3output priority encoder is implemented using FinFET design.

*Keywords*- FinFET, Priority Encoder, Power Delay Product, Energy Delay Product, Short Channel Effect, Sub threshold leakage current.

# I. INTRODUCTION

Nowadays, priority encoders have been widely utilized in high performance applications which persistently impose special design constraints in terms of low power consumption, high-frequency and minimum area. They provide considerable time savings in the area of On-chip testing, optical communications, and computer arithmetic applications<sup>[1]</sup>.Priority Encoders (PE) are commonly used in computer systems. Priority Encoder algorithm are used in number of computing components, such ascomparators<sup>[2]</sup>, fixed and floating point units<sup>[3]</sup>, increments, decrements<sup>[4]</sup> and interconnection network routers<sup>[5]</sup>, sequential address encoder of content addressable memories<sup>[6]</sup> are important sub-systems located on-chip or off-chip, which predominantly utilize the priority encoder function. As the computer systems data width gets longer and computer system become fasten, the speed of the Priority encoder becomes a key parameter in the performance of the computer system. At the same time, the overwhelming demand for compact electronics encourages the development of a power optimized Priority Encoder. Priority encoder function is to select only one request out of number of request at is input port and then selected input is been served by the system. The proposed priority encoder accepts 4 input request lines and sets only one of the outputs that correspond to the request that has the highest priority. In this paper we simulate 4:2 Priority Encoder using FinFET circuit at different voltages and calculate

different parameters of the circuit such as average power, leakage current, leakage power, delay and Power Delay product (PDP), Energy Delay Product (EDP). After comparing all simulation results at different voltage we found that on applying 0.3V to the circuit we get the better parameter in result.

# 1.1 FinFET

The term FinFET was invented by the University of California, Berkeley researchers to describe a non-planner, double-gate transistor built on an SOI (silicon on insulator) substrate, based on the earlier single gate transistor structure. The distinctive property of the FinFET is that the conducting channel is enfolded by a thin silicon "fin", that is forms the body of the device. The effective channel length of the deviceis determined by the width of the fin. Due to multi gate structure FinFET has full control over the channel and thus helps in reducing the Shot-Channel effect and also helps to overcome the Sub ThresholdLeakage Current problems of MOSFET devices.

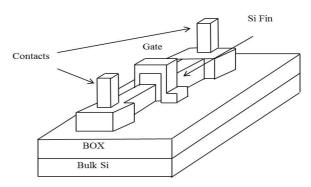

Figure1. Double Gate FinFET

The conventional Double Gate FinFET structure is shown in the figure1<sup>[7]</sup>. The tiny slab of undoped silicone perpendicular to the structure is the channel of the FinFET.

As the gate drain and source of the FinFET is doped with same type of dopant, so there is no p-n junction formation along the channel length and reduces the leakage current. The Higher mobility in the FinFET is due to the undoped channel, which eliminates the coulombs scattering<sup>[8]</sup>. The fraction of n-type to p-type mobility is higher in FinFET. In FinFET the source-body voltage variation did not affect the threshold voltage. This improvement in mobility and also

#### IJSART - Volume 5 Issue 3 -MARCH 2019

covers the way for extended series stacked transistors in the pull-down or pull-up networks of logic gates.

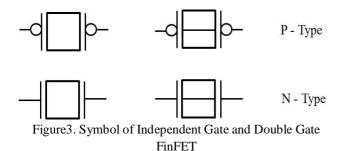

Independent Gate FinFET is shown in figure  $2^{[9-13]}$  is the double gate device in which the two Gate electrode are not connect together (the top portion of gate is etch out) and biased with different potential.MIGFET has many special features one of them is that the threshold voltage of one of the gates can be modified by the bias applied to the other gate. Here we present Priority Encoder circuit using double gate FinFET and the symbol for double gate FinFET is shown in figure  $3^{[14]}$ . Here the priority encoder is simulated on virtuoso tool of cadence at 45nm technology.

# II. PARAMETERS OF FINFET

#### 2.1 Sub threshold Leakage Current

When the transistor is switches from cut-off region to saturation region (Vgs > Vth) a channel formation is occurs which allows current ( $I_{ds}$ ) to flow between the drain and source. The current ( $I_{ds}$ ) from drain to source is given in the below equation

$$I_{ds} = \frac{\mu_{z} C_{ox} W_{eff}}{L} \left( V_{gs} - V_{th} \right) V_{ds} - \frac{V_{ds}^2}{2}$$

(1)

With  $\mu_n$  the charge-carrier effective mobility,  $W_{eff}$  the effective channel width and the L effective channel length. The effective channel width  $W_{eff}$  equals the channel width in First order approximation<sup>[12]</sup>.

#### 2.2 Power dissipation

Power dissipation is an addition of static power dynamic power and leakage power. But in most of the cases power dissipation depends on dynamic power. Hence it is given by

$$\mathbf{P}_{\text{total}} = \alpha_{\text{in}} \mathbf{I}_{\text{sc}} \mathbf{V}_{\text{dd}} \mathbf{f} \mathbf{T}_{\text{sc}} + \alpha \mathbf{V}_{\text{DD}}^2 \mathbf{f} \mathbf{C}_{\text{out}}$$

(2)

Page | 583

Equation 2 is clearly shows that the Power dissipation is depends on dynamic power and for low power dissipation<sup>[16]</sup> the static power must be less.

## Threshold voltage

Joining the gate work function, difference between the Gate and silicon fin, the increase in band gap and the increase in potential results in the following threshold voltage formula

$$V_{th} = V_{FB} + 2\alpha_B + \delta_W + \frac{qN_bX_{dep}}{C_{ex}(1-\frac{N_D}{L})(4)}$$

Where  $V_{FB}$  work function difference,  $\Phi_{B}$  surface potential at threshold voltage,  $\delta_{VF}$  is a fitting parameter introduced to take into account the changes <sup>[15, 17]</sup>.

#### **III. PRIORITY ENCODER**

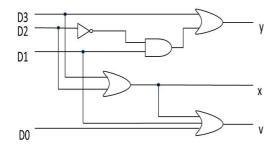

Priority as the name suggests means something that is more important than other and should be dealt with first (high /low priority). Priority Encoder does the same thing, whose way of providing output is similar to simple encoder with one advantage of selecting the operation with the priority function. With this facility of priority function, the input having highest priority is served first whenever choice has to make among more than one output. In addition to the two output x and y, the circuit has the third output denoted as V; this is a valid bit indicator that is set to 1 when one or more input are equal to 1, if all the input are 0, there is no valid input and V is equal to 0 and other two output are not correct and are denoted as don't care condition, the highest priority is given to the most significant bit (MSB) that is highest priority is given to the highest subscript number of the input, here we have the input D1 D2 D3 and D3 has the highest priority next is D2 and in the last D1 has the lowest priority. When D3 is 1, the output of x y is 11 (binary 3), regardless of the value so the other three lower priority input. When D2 is 1 the output xy is 10, provided that D3= 0, regardless of the value of the other two input. When D1 is 1 the output x y is 01, provided that D3 D2 = 00 and so on.

Figure.4 Circuit diagram of Priority Encoder

As we construct SG FinFET by shorting two P-types MOSFET and two N-type MOSFET to form P-type and N-type FinFET respectively and its logic diagram is shown in the figure No 3. The Priority Encoder is realized using the virtuoso tool of cadence. The spectra simulator of cadence is used to simulate the output. The gate of two PMOS or NMOS transistors are connected together to formed a FinFET like structure. Then FinFET using Priority encoder circuit is simulated by applying different voltages such as 0.3 V, 0.4 V, 0.45 V, 0.5 V, 0.6 V and 0.7 V respectively at 45 nm technology.

#### **IV. RESULTS**

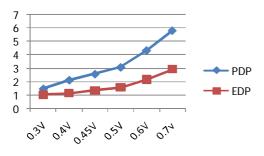

In this section, we present the simulation results of Priority Encoder at 45nm technology from virtuoso tool of cadence. Figure.5 shows the comparison among Energy Delay Product and Power Delay Product curves of DG FinFET at six differentpowersupplies at 45 nm technology respectively. At 45 nm technology the 4:3Priority encoder give better result at 0.3V that is Average Power is 2.071nW, Leakage Power is 54.39pW rather than at 0.7V that is Average Power is 11.6nW, and Leakage Power is 131.1pW. So, our experimental result gives minimum Delay and Average Power at 0.3V supply.

Figure 5. Veriatin of PDP and EDP with respect to voltage

## V. CONCLUSION

Page | 584

In this paper, we work on Priority Encoder by using FinFET. FinFET is one of the emerging technology used in various applications, has replaced many conventional CMOS based devices. Low power consumption is one of the basic need in forming any electronic device and for that purpose scaling is done which leads to leakage of current but that problem is tackled by using FinFET. In this paper, Average Power, Delay, Leakage Current and Leakage Power of FinFET based Priority Encoder at different voltage was examined and better result at 0.3V power supply is obtained. The Leakage Power, Average Power and Leakage Current were found to be 2.071 nW, 54.39 pW 13.74 pA respectively. Power Delay Product is 1.4641x10<sup>-16</sup> J and Energy Delay Product is 1.0249x10<sup>-22</sup>Js, than the 0.7V power supply in which the results are Average Power is 11.56nW, Leakage Power is 131.1pW and Leakage Current is 26.19pA, Power Delay Product is 5.8146x10<sup>-16</sup>J and Energy Delay Product is 2.9247x10<sup>-22</sup>Js. Here energy-delay product (EDP) is a useful metric for evaluating the quality of a design. As EDP is the product of PDP and Delay, PDP depends on Power supply. EDP has to be low, So EDP depends on the Delay (1/f) and the Power supply (V<sub>DD</sub>), so we can reduce EDP by reducing either Delay or Power supply or we can get the tradeoff between delay and power supply.

#### VI. AKNOLODGEMENT

The author would like to thanks ITM University, Gwalior for providing the cadence tool with collaboration of Cadence system design Bangalore for the work to be completed.

#### REFERENCES

- Summerville, D, H., Delgado-Frias, J, G. and Vassiliadis, S., "A flexible bit-pattern associative router for interconnection networks. IEEE Transaction of Parallel Distribute System", 7(5), 447–485 (1996).

- [2] Hennessy J, L. and D. A. Patterson, D, A. [Computer Architecture: A Quantitative Approach 3rd Edition], Morgan Kaufmann, New York (2002).

- [3] Huang, C, H. and Wang, J, S. "High-Performance and Power-Efficient CMOS Comparators", IEEE Journal of Solid-StateCircuits, 38(2) 254 -262 (2003)

- [4] Huang, C. H., Wang, J. S. and Huang, Y. C., "Design of High Performance CMOS Priority Encoders and Incremented/Decrements Using Multilevel Look ahead and Multilevel Folding Techniques", IEEE Journal of Solid-StateCircuits, 37(1) 63-76 (2002).

- [5] Delgado-Frias, J. G., Nyathi, J., Summerville, D. H., "A programmable dynamic interconnection router with

hidden refresh", IEEE Transaction onCircuits and Systems, Part I, 45(11) 1182-1190 (1998).

- [6] Kadota, H., Miyake, J., Nishimichi, Y., Kudoh, H., Kagawa, K.," An 8- Kbit content-addressable and reentrant memory", IEEE Journal of Solid-State Circuits, 20(5) 951-957(1985).

- [7] Sekigawa,T. and Hayashi, Y. [Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate]. Solid-State Electronics 27, 827 (1984)

- [8] Nuttinck, S., "double-gate FinFETs as a CMOS technology downscaling option: An RF perspective", IEEE Transaction on Electron Devices, 54(2), 279– 283(2007).

- [9] Mathew, L., Yang Du, A.V.-Y. Thean, Sadd, M., Vandooren, A., Parker, C., Stephens, T., Mora, R., Raghav Rai, Zavala, M., Sing, D., Kalpai, S., Hughes, J., Shimer, R., Jallepalli, S., Workman, G., White, B. E., Nguyen, B. Y., Mogab, A.,[Multi gated device architectures advances, advantages and challenges] International Conference on Integrated Circuit Design and Technology, 97(2004)

- [10] Zhang, W., Fossum, J. G., Mathew, L., Yang Du, [Physical insights regarding design and performance of independent-gate FinFETs], IEEE Transactions on Electron Devices 52-10, 2198 (2005)

- [11] Eminente, S., Kyoung-Il Na, Cristoloveanu, S., Mathew, L., Vandooren, A., "Lateral and vertical coupling effects in MIGFETs", Proceedings of the IEEE International SOI Conference, 94 (2005)

- [12] Endo, K., Liu, Y., Masahara, M., Matsukawa, T., O'uchi, S., Suzuki, E., Surdeanu, A., Witters, R. L., Doornbos, G., Nguyen, V. H., G. Van den bosch, Vrancken, C., Devriendt, K., Neuilly, F., Kunnen, E., Suzuki, E., Jurczak, M., Biesmans, S., [Independent double-gate FinFETs with asymmetric gate stacks], Microelectronic Engineering, 84-9/10, 2097 (2007)

- [13] Masahara, M., Surdeanu, R., Witters, L., Doornbos, G., Nguyen, V. H., Van den bosch, G., Vrancken, C., Devriendt, K., Neuilly, F., Kunnen, E., Suzuki, E., Jurczak, M., Biesmans, S., [Independent double-gate FinFETs with asymmetric gate stacks. Microelectronic Engineering] 84-9/10, 2097 (2007)

- [14] Dayal, A. and Akashe, S., "A novel double gate finfet transistor: optimized power and performance analysis for emerging nanotechnologies", Computing, Information Systems, Development Informatics & Allied Research 4, 4 December, 2013.

- [15] F. van Rossem, "Doping extraction in FinFET," University of Twente, Thesis 2009

- [16] Yu, B., Chang, L., S. Ahmed, H. Wang, S. Bell, Yang, C, Y., Tabery, C., C. Ho, Xiang, Q., T.-J. King et al.

"FinFET scaling to 10 nm gate length.In Electron Devices Meeting", IEEE International Conference on IEDM, 251– 254(2002)

[17] Poiroux, T., Vinet, M., Faynot, O., Widiez, J., Lolivier, J., Ernst, T., Previtali, B. and Deleonibus, S. "Multiple gate devices: advantages and challenges", Microelectronic Engineering, 80, 378–385 (2005)