# A Novel 15-Level Inverter Topology With Reduced Count of Switches

# Ashwini Ojha<sup>1</sup>, Praveen Bansal<sup>2</sup>

<sup>1, 2</sup> Madhav Institute of technology and Science, Gwalior(M.P)

Abstract- This paper introduces a new multilevel converter topology, which can synthesize all possible additive and subtractive combinations of input DC levels in the output voltage waveform with fewer power electronic switches. An appropriate modulation scheme has also been proposed for high switching frequency operation of the proposed topology. As compared with the classic multilevel topologies, the proposed topology results in reduction of the number of switches and conduction losses. The operation and performance of the proposed multilevel converter has been ascertained through simulation. A 15-level inverter with asymmetric source configuration has been presented or using the proposed modulation scheme. The results are verified using MATLAB/SIMULATION environment.

*Keywords*- Multilevel inverter(MLI), APOD, POD, Total harmonic distortion(THD).

# I. INTRODUCTION

A multilevel inverter produces a staircase waveform with the help of proper connection of switches and input DC voltages i.e. battery. Regulated switching of semiconductor devices plays an important role to achieve a multilevel waveform with controlled amplitude of waveform, and frequency[1-4]. This approach of DC to AC conversion offers a number of advantages over conventional inverters, such as: capability to operate at higher voltages using traditional semiconductors, reduced common mode voltages, and reduced dv/dt stresses, staircase waveform with better harmonic profile, smaller filter requirements, flexibility to operate on low- and high switching frequencies. As a result, multilevel inverters nowadays attract attention in high-power and highapplications. Although voltage/medium-power classical multilevel topologies such as Diode clamped clamped (DCMLI) converters [5], flying capacitors (FCMLI) converters [6] and cascaded H-bridge (CHBMLI) converters [7] have been commercialized, but device count becomes significantly high when they are to be designed for higher number of voltage levels. This introduces complexity in design and increase of cost. Therefore new topologies are being proposed and reduce the overall count of active and passive devices for power conversion [8-10]. However, reducing the number of devices involves one or more of

Page | 846

following compromises: increased power rating of semiconductor devices, increased number of power sources, and complex modulation schemes. In spite of these compromises, there is still a possibility of exploring topological structures which can maximize the number of levels with given input DC sources.

In this paper, a multilevel inverter topology is proposed, which is capable of synthesizing all possible additive and subtractive combinations of the input DC levels. The proposed topology bears functional similarity to the CHB topology in two ways: first, it needs multiple isolated input DC voltages; and secondly, it offers the possibility of combining the input DC voltage levels into all additive and subtractive values. An important advantage of the proposed topology over the conventional topologies topology is in terms of ON state losses which are reduced considerably. The topology can be explored for various industrial i.e. grid interfacing of renewable energy sources (e.g. photovoltaic energy) [11], static synchronous compensators (STATCOMs) speed control of drives etc.

# II. PROPOSED 15-LEVEL MULTILEVEL INVERTER TOPOLOGY

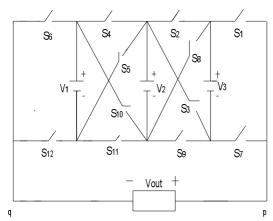

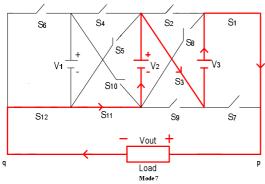

The proposed topology aims at synthesizing all possible combinations that can be attained through additions and subtractions of input DC voltage levels as described below in Fig.1.This topology is have reduced number of switch count and produces output voltage of 15-level output. Possible output voltage levels for  $V_1=13$ , V2=39 and  $V_3=39$  are 13V,26V, 39V,52V,65V,78V,91V,0V,-13V,-26V,-39V,-52V,-65V,-78Vand -91V.

Fig.1 Proposed 15-Level MLI

| Output Level | Corresponding<br>Voltage value                  | Switches in ON<br>state |

|--------------|-------------------------------------------------|-------------------------|

| 0            | 0                                               | S1,S2,S4,S6             |

| 1            | V3 =13                                          | S1,S2,S4,S12            |

| 2            | V1-V3=26                                        | S1,S9,S6,S11            |

| 3            | V1=39                                           | S1,S9,S12,S11           |

| 4            | V1+V3=52                                        | S1,S3,S4,S11            |

| 5            | V1+V2-V3=65                                     | S1,S3,S11,S6            |

| 6            | V <sub>1</sub> +V <sub>2</sub> =78              | S1,S3,S11,S12           |

| 7            | V1+V2+V3                                        | S1,S3,S5,S12            |

| -1           | -V1                                             | S7,S9,S11,S6            |

| -2           | V3-V1                                           | S7,S2.S4,S12            |

| -3           | -V1                                             | S7, S2, S4, S6          |

| -4           | -V1-V3                                          | S7, S8, S11, S6         |

| -5           | -V <sub>1</sub> -V <sub>2</sub> -V <sub>3</sub> | S7,S8,S4,S12            |

| -6           | -V <sub>1</sub> -V <sub>2</sub>                 | S7,S8.S4,S6             |

| -7           | -V1-V2-V3                                       | S7,S8,S10,S6            |

Table I: Look Up table for 15-Level Inverter topology

With such combinations of switches applications 15 level of output voltage is produced. Relevant look up table is shown with switching combinations for 15-level of output voltage production. For one level of output four switches are turned ON can be seen through table I.

# III. WORKING OF PROPOSED TOPOLOGY

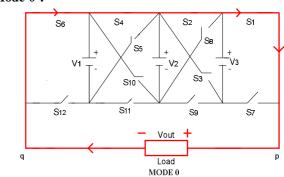

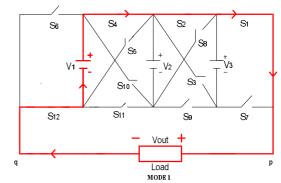

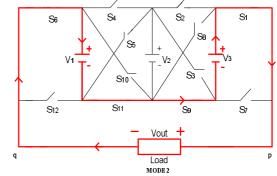

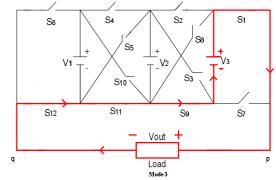

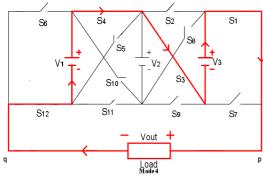

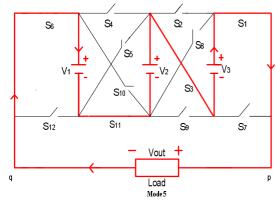

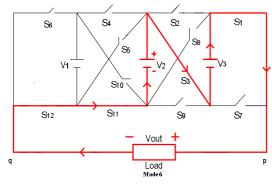

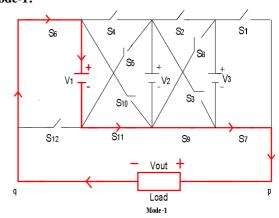

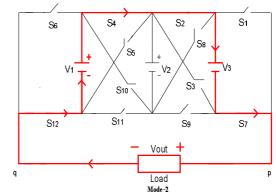

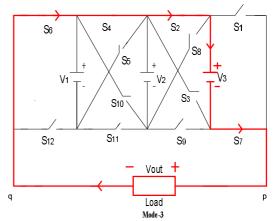

In this section operating modes of propose topology is introduced. From Fig.2 all operating modes are explained through relevant diagrams.

Mode '1':

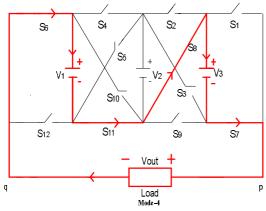

Mode 4:

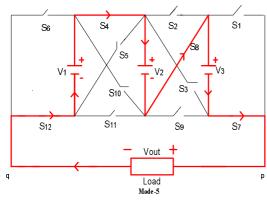

Mode 5:

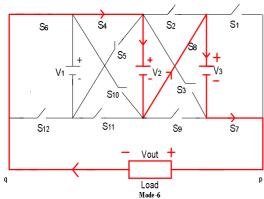

Mode 6:

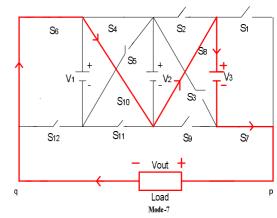

Mode 7:

Mode-1:

Mode -2:

Mode -3:

Page | 848

www.ijsart.com

# Mode-4:

Fig.2 Operating modes of 15-level inverter

#### Mode -5:

### Mode-6:

Mode -7

# **IV. MULTICARRIER PWM SCHEMES**

Carrier shifting techniques:

- a) Phase Disposition (PD)[12]

- b) Phase Opposition Disposition (POD)[13]

- c) Alternate Phase opposition Disposition (APOD)

All these techniques employed in proposed topology and these are high carrier frequency triangular wave with reference is sinusoidal wave.

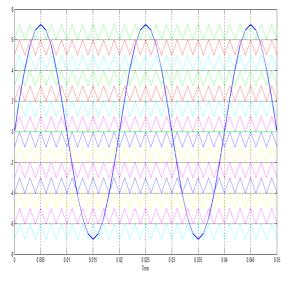

# 4.1Phase Disposition (PD):

In this technique alternate waves are shifted from one other by magnitude of '1'. All the triangular carriers are in phase and compared with sinusoidal reference wave. Sine reference is compared with carrier wave and output pulse is obtained at reference wave magnitude is more than carrier wave.

Fig.3 PD technique waveform

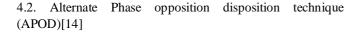

In this technique alternate waves phase shifted by 180 degrees and disposed from each other by '1'.Sine wave is reference and triangular wave is high frequency wave which is to be compared. Output is obtained at instant where reference wave magnitude is more than carrier wave.

Fig.4 APOD technique waveform

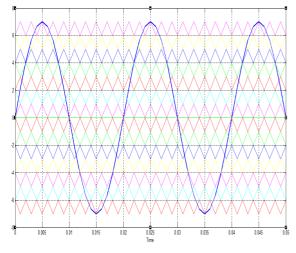

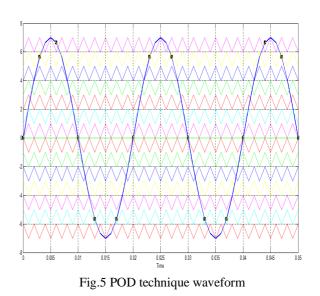

# 4.3 Phase Opposition Disposition Technique (POD)

In this technique positive and negative side of reference line is phase shifted by 180 degrees. Sine reference is compared with carrier wave of high frequency .Output pulse is obtained when sine reference is more than carrier wave.

# V. RESULTS

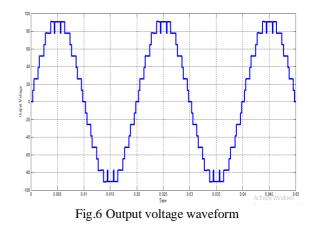

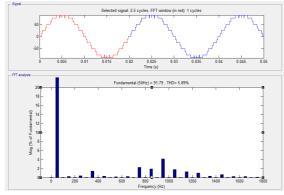

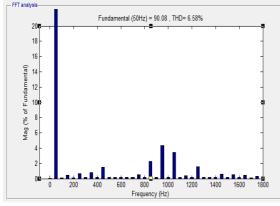

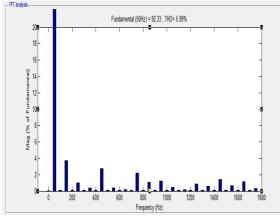

THD i.e. total harmonic distortion is parameter used to ascertain quality of inverter if THD is less then efficiency will be high, insulation losses are less and harmonic components i.e. third harmonic is less and can be filtered easily with small filter. It can be easily ascertained that PD techniques offers least THD OF 5.89% hence it is best suited for proposed topology. Whereas APOD and Pod offers high THD hence reduced efficiency is achieved by these modulation schemes .FFT analysis are shown from Fig.7 to Fig.9 of PD,POD and APOD respectively. Output voltage waveform is shown in Fig.6 having staircase waveform of 15 levels. Table II shows respective THD values for various modulation schemes at different modulation indices. Further Table III shows comparison of propose topology with conventional schemes of same level of output.

Fig.7 FFT analysis of PD Technique at ma==1

Fig.8 FFT analysis of POD technique at ma=1

Fig.9 FFT analysis of APOD technique at ma=1

Table II:THD for various techniques at various modulation indices

| Modulation<br>technique | Modulation index(m <sub>s</sub> ) |       |         |       |

|-------------------------|-----------------------------------|-------|---------|-------|

|                         | 1 (                               | 0.95  | 0.9 0.1 | 87    |

| PD                      | 5.89%                             | 8.15% | 8.34%   | 8.27% |

| POD                     | 6.58%                             | 7.44% | 8.02%   | 8.89% |

| APOD                    | 5.99%                             | 8.71% | 8.78%   | 9.31% |

Table III: Comparison of device requirement of conventional to proposed topology

|            | 1 1   | T          | 05  |          |

|------------|-------|------------|-----|----------|

| Inverter   | DCMLI | Flying     | CHB | Proposed |

| topology   |       | capacitors |     | topology |

| Main       | 28    | 28         | 28  | 12       |

| switches   |       |            |     |          |

| Clamping   | 182   | 0          | 0   | 0        |

| diodes     |       |            |     |          |

| DC bus     | 14    | 14         | 0   | 0        |

| capacitors |       |            |     |          |

| Total      | 224   | 42         | 28  | 12       |

| components |       |            |     |          |

#### VI. CONCLUSION

It can be well conclude that by increasing no of levels of inverter better wave shape near to sinusoidal is produced having low distortion.THD is considerably reduced by applying multicarrier PWM schemes. More efficient inverter with reduced count of switches than conventional topologies is synthesized. With less count of switches switching losses are reduced and gate driver requirement is reduced.

#### REFERENCES

- Barros, J.D., Silva, J.F.: 'Optimal predictive control of three-phase NPC multilevel converter for power quality applications', IEEE Trans. Ind. Electron., 2008, 55, (10), pp. 3670–3681.

- [2] Lin, L., Zou, Y., Wang, Z., Jin, H.: 'Modeling and control of neutral point voltage balancing problem in three-level NPC PWM inverters'. Proc. 36th IEEE PESC, Recife, Brazil, June 2005, pp. 861–866.

- [3] Rodriguez, J., Lai, J.S., Peng, F.Z.: 'Multilevel inverters: a survey of topologies, controls, and applications', IEEE Trans. Ind. Electron, 2002, 49, (4), pp. 724–738.

- [4] Rodriguez, J., Franquelo, L.G., Kouro, S., et al.: 'Multilevel converters: an enabling technology for highpower applications', Proc. IEEE, 2009,97, (11), pp. 1786– 1817.

- [5] Jose Rodriguez, Jih-Sheng Lai and Fang Zheng Peng. "Multilevel Inverters: A survey of topologies, controls and applications." IEEE Trans. Ind.Electronics.vol-49 no.4, pp 724-738, Aug. 2002.

#### IJSART - Volume 4 Issue 7 - JULY 2018

- [6] X.Yuan and I.Barbi, "Fundamentals of a New Diode Clamping Multilevel Inverters", IEEE Transaction Power.Electron., Vol.15, No.4, 2000, pp.711-718.

- [7] Peng, F.Z., Lai, J.S., Mckeever, J.W., Vancoevering, J.:

'A multilevel voltage–source inverter with separate DC sources for static var generation', IEEE Trans. Ind. Appl., 1996, 32, (5), pp. 1130–1138.

- [8] Ounejjar, Y., Al-Haddad, K., Gre´goire, L.A.: 'Packed U cells multilevel converter topology: theoretical study and experimental validation', IEEE Trans. Ind. Electron., 2011, 58, (4), pp. 1294–1306.

- [9] Chaturvedi , P.K., Jain, S., Agarwal, P.: 'A simple carrier based neutral point potential regulator for 3-level diode clamped inverter', Int. J. Power Electron, 2011, 3, (1), pp. 1–25.

- [10] Babaei, E.: 'A cascade multilevel converter topology with reduced number of switches', IEEE Trans. Power Electron., 2008, 23, (6), pp. 2657–2664.

- [11] Tolbert, L.M., Peng, F.Z.: 'Multilevel converters as a utility interface for renewable energy systems'. IEEE Power Engineering Society Summer Meeting, 2000, vol. 2, pp. 1271–1274.

- [12] B.P.McGrath and Holmes, "Multicarrier PWM strategies for multilevel inverter," IEEE Trans.Ind-Electron.,vol.49,no.4, Aug.2002, pp.858,867.

- [13] M. Manjrekar and G. Venkataramanan, "Advanced topologies and modulation strategies for multilevel inverters," in Proc. IEEE PESC'96, Baveno, Italy, June 1996, pp. 1013–1018.

- [14] L.M. Tolber, T.G.Habetler, "Novel Multilevel Inverter Carrier based PWM Method," IEEE Ind.Appli.,vol.35. Sep/Oct 1999, pp.1098 -1107.

Ashwini Ojha was born in 17 march 1991 in Jhansi. He received his B.Tech degree from Babu Banarsidas National Institute of Technology and Management, Lucknow (U.P)in 2014 and currently pursuing M.E. with specialization in Industrial systems and drives from Madhav Institute of Technology and Science (MITS, Gwalior) in Gwalior (2016-2018).

Praveen Bansal obtained his bachelor of Engineering (Hon's) in Electrical Engineering from Madhav Institute of Technology and Science(MITS),Gwalior in 2009,MTech degree in Electrical Drives from Maulana Azad National Institute of Technology in 2012,Currently he is an Assistant Professor at MITS, Gwalior. His area of interests includes multilevel Inverters, Induction motor modeling, and PWM techniques