# A Switch Ladder Topology For 31-Level Multilevel Inverter With Different PWM Techniques

Deepak Singh<sup>1</sup>, Praveen Bansal<sup>2</sup>

<sup>1, 2</sup> Dept of Electrical Engineering <sup>1, 2</sup> Madhav Institute of Technology & science Gwalior, India

Abstract- The demand of multi-level inverter has been expanded due to their high power practical application and the capability for getting just about a sinusoidal output voltage liken to conventional two level inverter. This paper orient to develop a new variety of switch ladder multilevel inverter configuration for generations of thirty one levels of output voltage.

This proposed multilevel inverter topology here is implemented with different pulse width modulation (PWM) techniques, which involve less count of power switches and voltage sources to bring down the complexness of a circuit as compare to other multilevel inverter configurations. A multicarrier PWM technique is used to generate 31-level output voltage. MATLAB/simulation is used to simulate the results of a 7-level multilevel inverter topology.

*Keywords*- multilevel inverter (MLI), thirty one level inverter, asymmetric topology, total harmonic distortion (THD), multicarrier pulse width modulation.

### I. INTRODUCTION

In recent decades with the improvement of power semiconductor engineering, multilevel inverter (MLI) have obtained enormous popularity in researches as well as in industries owing to role in high power and high voltage practicle applications [7]. The commencement of the word " multilevel inverter " was recorded in year 1970s and 1980s. The introductory unit of a multilevel inverter is called three level. It is similar to a square wave form [3]. The some major applications areas of multilevel invertor are : high power medium voltage drives, HVDC transmission, distributed generations, electrical vehicular technology, static VAR compensator, induction heating, stand by air - craft power supplies, UPS (uninterruptable power supplies) for computer[2]. The advantages to use a multilevel inverter than a two level inverters configurations are decrease total harmonic distortion (THD), decrease dv/dt stress across devices, less electromagnetic interference (EMI), less common mode voltage and improve use of rail voltage etc [4].

Several multilevel topologies have been classified as the diode clamped multilevel inverter (DCMLI), the flying capacitor multilevel inverter (FCMLI), the cascaded H-bridge multilevel inverter (CHBMLI) [6]. The diode clamped and flying capacitor converter configurations function with the single DC source but the number of device increase parabolically with the number of output levels raises production cost and complicated control.

This paper present a new 31-level topology of switch ladder multilevel inverter configuration in section II, using fixed frequency level shifted carrier based pulse width modulation techniques which require for decrease deformation of sinusoidal voltage and less number of power switches.

## **II. PROPOSED MULTILEVEL INVERTER**

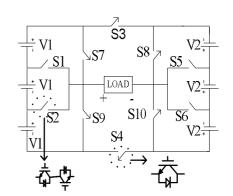

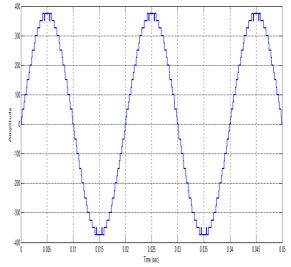

The proposed switch ladder 31 level multilevel inverter (SLMI) is shown in figure 2.1. In this circuit there are six unidirectional switches (S3, S4, S7, S8, S9, S10), four bidirectional switches (S1, S2,S5,S6), and six DC sources in which two have same magnitude V1 and other two have V2. The values of dc sources are V1= 25V and V2 = 100V. The values of output voltages frequency is 50 Hz. The R-L load with the values of R= 108  $\Omega$  and L = 45mH is used for this topology. It is clear that the maximum output voltage is 375V. Fig. 5.1 shows the output voltage of 31level inverter. The levels

are:0v,±25v,±50v,±75v,±100v,±125v,±150v,±175v,±200v,±22 5v,±250v,±275v,±300v,±325v,±350v,±375v.

Fig. 2.1 SWITCH LADDER MULTILEVEL INVETER

## IJSART - Volume 4 Issue 7 – JULY 2018

TABLE 1 shows the value of output voltages (Vo) for the different states of S1, S2, S3, S4, S5, S6, S7, S8, S9 and S10 Switches

| Switches. |                                   |        |        |         |        |        |        |   |   |             |      |

|-----------|-----------------------------------|--------|--------|---------|--------|--------|--------|---|---|-------------|------|

| N         | Switches States (I - ON, 0 - Off) |        |        |         |        |        |        |   |   |             | 16   |

| a.        | s<br>1                            | 8<br>2 | S<br>3 | \$<br>4 | 5<br>5 | S<br>Ó | S<br>7 | 8 | 8 | S<br>1<br>0 |      |

| 1         | 0                                 | 0      | 1      | 0       | 0      | 0      | 1      | 1 | 0 | 0           | 0    |

| 2         | 0                                 | 1      | 0      | 1       | 0      | 0      | 0      | 0 | 0 | 1           | 25   |

| 3         | 1                                 | 0      | 1      | 0       | 0      | 0      | 0      | 1 | 0 | 0           | -25  |

| 4         | 1                                 | 0      | ٥      | 1       | 0      | 0      | 0      | 0 | 0 | 1           | 50   |

| 5         | 0                                 | 1      | 1      | 0       | 0      | 0      | 0      | 1 | 0 | 0           | -50  |

| 6         | 0                                 | 0      | 0      | 1       | 0      | 0      | 1      | 0 | 0 | 1           | 75   |

| 7         | ٥                                 | 0      | 1      | ٥       | ٥      | ٥      | ٥      | 1 | 1 | 0           | -75  |

| 8         | 0                                 | 0      | 0      | 1       | 0      | 1      | 0      | 0 | 1 | 0           | 100  |

| 9         | 0                                 | 0      | 1      | 0       | 1      | 0      | 1      | 0 | 0 | 0           | -100 |

| 10        | 0                                 | 1      | 0      | 1       | 0      | 1      | 0      | 0 | 0 | 0           | 125  |

| п         | 1                                 | 0      | 3      | 0       | 5      | 0      | 0      | 0 | 0 | 0           | -125 |

| 12        | 1                                 | 0      | 0      | 0       | 1      | 0      | 1      | 0 | 0 | 0           | 150  |

| В         | 0                                 | 1      | 1      | 0       | 1      | 0      | 0      | 0 | 0 | 0           | -150 |

| 14        | 0                                 | 0      | 0      | 1       | 0      | 1      | 1      | 0 | 0 | 0           | 175  |

| 15        | 0                                 | 0      | 1      | 0       | 1      | 0      | 0      | 0 | 1 | 0           | -175 |

| 16        | 0                                 | 0      | 0      | 1       | 1      | 0      | 0      | 0 | 1 | 0           | 200  |

| 17        | 0                                 | 0      | 1      | 0       | 0      | 1      | 1      | 0 | 0 | 0           | -200 |

| 18        | 0                                 | 1      | 0      | 1       | 1      | 0      | 0      | 0 | 0 | 0           | 225  |

| 19        | 1                                 | 0      | 1      | 0       | 0      | 1      | 0      | 0 | 0 | 0           | -225 |

| 20        | 1                                 | 0      | 0      | 1       | 1      | 0      | 0      | 0 | 0 | 0           | 250  |

| 21        | 0                                 | 1      | 1      | 0       | 0      | 1      | 0      | 0 | 0 | 0           | -250 |

| 23        | 0                                 | 0      | 1      | 0       | 0      | 1      | 0      | 0 | 1 | 0           | -275 |

| 24        | 0                                 | 0      | 0      | 1       | 0      | 0      | 0      | 1 | + | 0           | 300  |

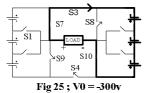

| 25        | 0                                 | 0      | 1      | 0       | 0      | 0      | 1      | 0 | 0 | 1           | -300 |

| 26        | 0                                 | Ť      | •      | Ť       | 0      | 0      | 0      | 1 | 0 | 0           | 325  |

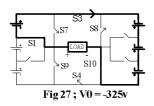

| 27        | Ť                                 | 0      | Ť      | 0       | 0      | 0      | 0      | 0 | 0 | Ť           | -325 |

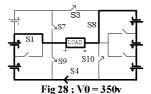

| 28        | 1                                 | 0      | 0      | 1       | 0      | 0      | 0      | 1 | 0 | 0           | 350  |

| 29        | 0                                 | 1      | 1      | 0       | 0      | 0      | 0      | 0 | 0 | 1           | -350 |

| 30        | 0                                 | 0      | 0      | 1       | 0      | 0      | 1      | 1 | 0 | 0           | 375  |

| п         | 0                                 | 0      | 0      | 1       | 0      | 0      | 0      | 0 | 1 | 1           | -375 |

|           |                                   |        |        |         |        |        |        |   |   |             |      |

The number of output voltage levels and the

Number of bidirectional switch and value of DC sources V1 and V2 are obtained as follows,

| V1 = Vdc            | (1) |

|---------------------|-----|

| V2 = (n) Vdc        | (2) |

| Vo = (n-1)(V1 + V2) | (3) |

Where n represent the no. of bidirectional switch in SLMI.

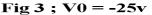

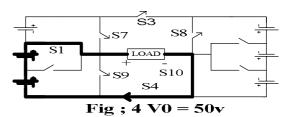

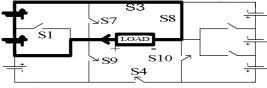

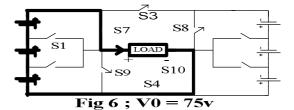

## **III. OPERATING MODES**

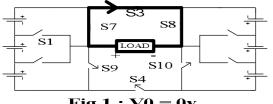

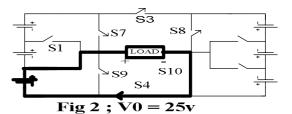

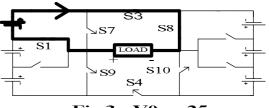

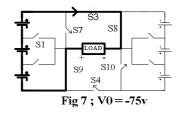

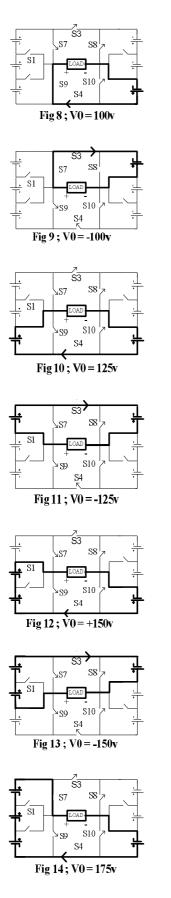

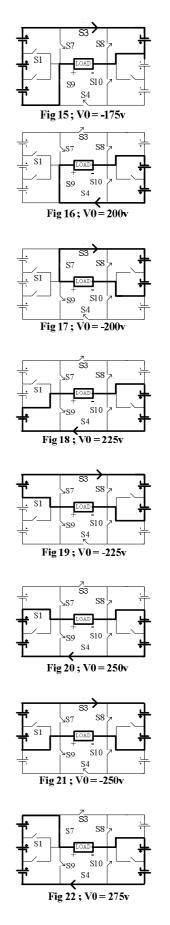

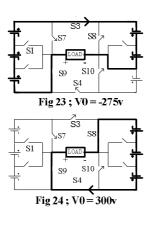

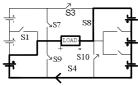

Various operating modes to obtain different voltage levels are shown in the following figures.

Figure 3.1 shows the different operating modes of switch Ladder 31- level Multilevel Inverter.

Fig 5 ; V0 = -50v

www.ijsart.com

www.ijsart.com

Fig 26 ; V0 = 325v

Fig 31; V0=-375v

Fig 3.1(Fig 1 – fig 31) shows Different operating modes of proposed MLI

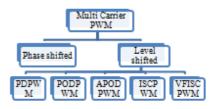

## **IV. MULTICARRIER PWM**

Different types of MCPWM modulation techniques are

The entire above multicarrier pulse width modulation techniques are use in high frequency switching.

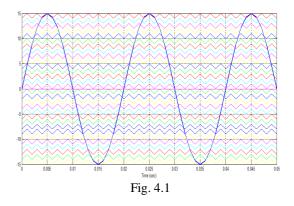

• **PHASE DISPOSITION (PD) TECHNIQUE** In PD technique all carrier waveform are superimposed over one another like layer with same phase, amplitude and frequency as shown in figure 4.1

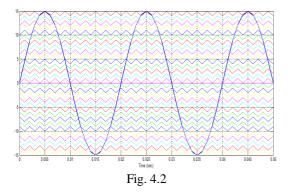

## PHASE OPPOSITION DISPOSITION (POD)TECHNIQUE

In POD technique the carrier waveforms above or below the zero reference are phase shifted by 180 degree as shown in figure 4.2 IJSART - Volume 4 Issue 7 – JULY 2018

#### ISSN [ONLINE]: 2395-1052

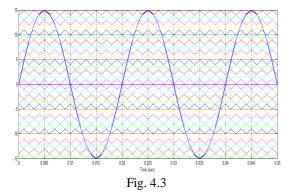

• ALTERNATIVE PHASE OPPOSITION DISPOSITION (APOD -PWM) TECHNIQUE In APOD technique all the adjacent carriers are 180 degree out of phase from each other on either side of zero reference level as shown in figure 4.3

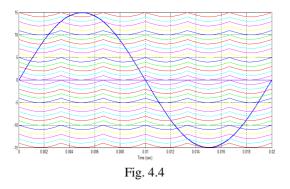

• **INVERTED SINE CARRIER PWM TECHNIOUE** In ISCPWM technique inverted sine wave of certain constant frequency acts as a carrier signal as shown in figure 4.4

V. SIMULATION RESULT

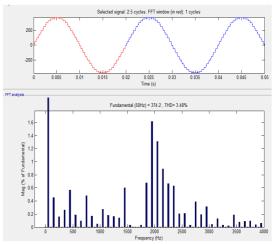

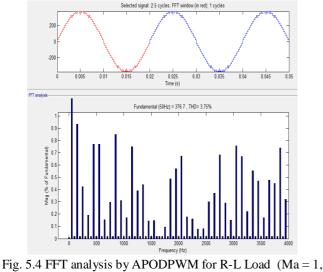

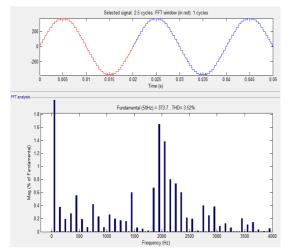

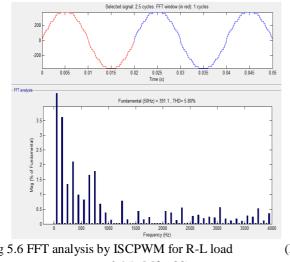

Multiple Modulation techniques is presented for proposed inverter topology and it has found out that by increasing the output voltage level THD can be considerably reduced. THD depicts the harmonic contents in the output voltage wave and by increasing the levels of output voltage, we can reduce THD and associate losses, thereby increasing efficiency. FFT analysis is shown for various modulation schemes from Fig. 5.3 to Fig. 5.6. On application of POD technique at  $m_a$ =1 THD is 3.48%, and for PD, APOD and ISCPWM technique at  $m_a$ =1 THD is 3.52% 3.75%, 6.38% respectively. Thus POD technique minimize the THD to 3.48% is as per IEEE standard 519 and it is best suited for proposed topology.

Fig.5.1 Output Voltage waveform for a 31 level MLI

Fig. 5.2 Voltage waveform of bidirectional switches S1 and S5

Fig. 5.3 FFT analysis by PODPWM for RL load (Ma= 1, Mf= 80)

### ISSN [ONLINE]: 2395-1052

Mf = 80)

Fig. 5.5 FFT analysis by PDPWM for R-L Load (Ma = 1, Mf = 80)

Fig 5.6 FFT analysis by ISCPWM for R-L load (Ma =0.95, Mf = 80)

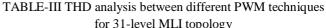

| for 31-level MLI topology   |       |      |      |      |      |  |  |  |

|-----------------------------|-------|------|------|------|------|--|--|--|

| SCHEMES                     | % THD |      |      |      |      |  |  |  |

| MODULATION<br>INDICIES (MI) | 1     | 0.95 | 0.9  | 0.85 | 0.8  |  |  |  |

| PD                          | 3.52  | 3.99 | 4.69 | 4.53 | 4.91 |  |  |  |

| POD                         | 3.48  | 4.05 | 4.64 | 4.44 | 4.84 |  |  |  |

| APOD                        | 3.75  | 4.28 | 4.88 | 5.12 | 4.80 |  |  |  |

| ISCPWM                      | 6.38  | 5.80 | 6.23 | 6.61 | 6.54 |  |  |  |

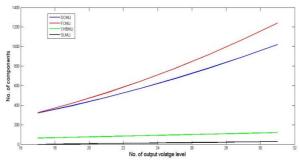

Fig. 5.7 Comparison between different multilevel inverter topologies

## VI. CONCLUSION

In this paper 31-level Switch Ladder multi-level inverter topology is proposed with different PWM techniques and it is being found that the SLMLI is the too encouraging choice for industry application. The switching operation of this topology requires less number of switches, less gate drive circuits and higher reliability as compared to conventional MLI topologies. It can be seen that the different PWM techniques reduce the harmonics. Phase opposition disposition (POD) technique to reduce THD of 3.48% and obtain nearer sine wave.

#### REFERENCES

- [1] A. Ajami, M. R. J. Oskuee, A. Mokhberdoran and A. V. Bossche, "Developed cascaded multilevel inverter topology to minimise the number of circuit devices and voltage stresses of switches," IET Power Electron., vol. 7, iss. 2, pp. 459-466, 2014.

- [2] Jose Rodriguez, Jih-Sheng Lai and Fang Zheng Peng. "Multilevel Inverters: A survey of topologies, controls and applications." IEEE Trans. Ind.Eletronics.vol-49 no.4 pp 724-738, Aug. 2002.

- [3] A. Nabae, I. Takahashi, and H. Akagi, "A new neutralpointclamped PWM inverter," IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [4] J. Ebrahimi, E. Babaei, G.B. Gharehpetion, A new Multilevel converter topology with reduced number of

Power electronic components, IEEE Trans. Power Electron.59 (2) (2012) 655-667.

- [5] J. Rodriguez, S. Bernet, B.wu, J.pontt, and s.kouro, "Multilevel voltage- Source converter topologies for Industrial mediumvoltage drives" IEEE. Trans. Ind. Electron, vol.54, no 6, pp.2930-2945 Dec 2007.

- [6] Panagis, P.; Stergiopoulos, F.; Marabeas, P.; Manias, S.;

"Comparison of state of the art multilevel inverters," Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, vol.,no., pp.4296-4301, 15-19 June 2008.

- [7] H. Stemmler. "Power electronics in electric traction applications," IEEE conference of Industrial Electronics, Control and Instrumentation, IECON'93, 2:7 07 – 713, 1993.

Deepak Singh was born in Mathura, India. He Received B.Tech Degree in Electrical Engineering from UPTU, Lucknow, India, currently he is doing M.E. at the Department of electrical engineering, M.I.T.S. Gwalior, India since 2016. His area of interest in the power electronics, Multilevel Inverter.

Praveen Bansal born in Gwalior, India. He Received B.E. Degree in Electrical Engineering from M.I.T.S Gwalior, India in 2009 with Honours. He is received M.Tech degree in electrical drives From M.N.I.T. Bhopal, India in 2012.Currently he is Assistant Professor in M.I.T.S Gwalior, India .His area of interest in power electronics and drives.