# A Back Gated, Ultra Low Power, Better Phase Noise Voltage Control Oscillator For Multi-Standard Wireless Communication Protocol

Harshal Chauhan<sup>1</sup>, Asst. Prof. Vinod Sonkar<sup>2</sup> <sup>1, 2</sup> Dept of EC <sup>1, 2</sup> SDBCT Indore

Abstract- Since VCO is the important part for any receiver, it need to be design in such a way that it justify all the parameter such as low power consumption, low phase noise, tuning range, FOM. Low power consumption depends on low supply and current consumption by whole circuit. Low phase noise and FOM depend upon the transistor design, device size and tuning range depend on MOS varactor. It is very difficult to obtain low phase noise since it depends on quality factor and all the devices connected in the circuit and the value of inductor is chosen in such a way that it can generate require frequency range. So, in this thesis, VCO consist of eight transistor connected in compounded pair which in turn are connected in cross coupling. NMOS transistor is bulk bias to reduce the power consumption. This reduces the phase noise which is very important for any VCO. The whole circuit is working at 1.2 V supply which consume 3.9 mW of power. This VCO has frequency range of 5.0-7.35 GHz and is design for wireless standard communication protocol such as 802.11 a/g/n. This circuit achieve phase noise of -118.84 dBc/Hz and figure of merit of -197 dBc/Hz.

*Keywords*- VCO, Phase Noise, FOM, Tuning Range, Low Power, Bulk Bias.

# I. INTRODUCTION

VCO are widely used in instrumentation and communication systems. Technical evolution and market requirements demand for High frequency generation.vco are also used in pacemaker. A voltage-controlled oscillator or VCO is an electronic oscillator designed to be controlled in oscillation frequency by an input voltage.

In recent years, there has been a strong growth in the modern wireless data and voice communication standards in numerous frequency bands. Modern transceivers for the wireless communication consist of many building blocks, such as low-noise amplifiers (LNAs), mixers, frequency synthesizers (FS), filters and amplifiers. With the advancement of radio frequency (RF) technology and requirement for more integration, new RF wireless architectures are needed. There is a tremendous demand of mobile communication and wireless communication systems in today's modern life. This has placed certain limitations and requirements on the communication channel bandwidths and spacing. The modern wireless communication systems rely strongly on frequency conversion and switching of one frequency band to other frequency bands.

Frequency synthesizer is one of the most critical components in the wireless transceiver. It greatly affects the overall performance of the wireless transceiver system. Frequency synthesizers are commonly used as a local oscillator (LO) in the wireless transceivers for frequency translation and channel selection.

The key idea is to down convert the RF signal to the baseband signal and it is also known as direct conversion or zero-IF receiver.

To avoid the loss of information, the down conversion must provide quadrature outputs for the frequency and phase modulated signals. Therefore, frequency synthesizer requires the accurate quadrature signal generation from local oscillator (LO). RF transceivers require quadrature signal and quadrature voltage controlled oscillator (QV CO) provides the best solution for the generation of the quadrature signal.

# **II. LITERATURE REVIEW**

Dixit and his friends[15] demonstrate the difference between IMOS and DSB based LC VCO configuration. They have design LC VCO for 5-5.47 GHz oscillation frequency.they have also shown the design tradeoff to obtain better VCO.

Ji and friends[16] introduce self biased VCO in which push pull configuration with resistor is used. This method improves amplitude response and reduce tank loading.

## IJSART - Volume 4 Issue 6 - JUNE 2018

This also reduce the need of choke inductor which require large space of chip. This circuit is implemented on 65nm.

Sadhu[17] achieved tuning range of 87.2 % by using switching inductor technique to design VCO with frequency from 3.3 to 8.4 GHz. Power consume by this design was 6.5 and 15.4 mW.

Hsu and his mates[18] show how to improve the phase noise of VCO and also shown Q enhancement technique. They design body biased VCO that help in reducing power consumption. This circuit is designed on 180 nm technology.

Zhou[19] designed dual band VCO for frequency range from 0.4-6 GHz that covers wireless standard such as WCDMA,GSM,Bluetooth and WLAN. They design this VCO on 130 nm technology which consume 34-77 mW of power. Xiangning Fan and his friends[20] use switched capacitor array to extend the frequency range and output buffer to drive the output signal and prevent from external intereference. With this circuit arrangement , they achieved -108 dBc/Hz of phase noise at 1 MHz offset.

$Mehrabian [21] \ use \ active \ inductor \ concept \ which \ is tuned \ with \ the \ help \ of \ active \ resistor \ and \ achieved \ tuning \ range \ of \ 3.8-7.4 \ GHz$ . with this design,-92.05 dBc/Hz of phase noise is obtained.

Hegazi[22] found that the phase noise can be increase by adding extra LC filter to the circuit. To prove this concept, he deisgned three VCO. Out of these three, two are working at 1.1 GHz and one at 2.1 GHz.

Sani and his friend[23] proposed cascade technique that allow current scalable design at low supply voltage, without dissipating extra power and without effecting output voltage swing.they have designed on 65 nm technology and 1 V supply is used.

Siddharth Bhat[24] use bulk driven technique in which input voltage is applied at the bulk of PMOS transistor. Input voltage range was 0-1 V and 0.4 V of supply is used. With this technique, whole circuit consume  $350 \,\mu$ W.

## **III. THEORY**

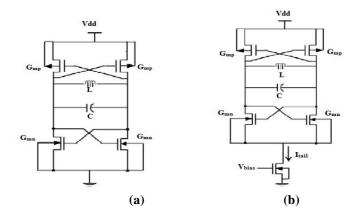

CMOS cross coupled topology has a NMOS cross coupled differential pair, LC tank and in addition to this a differential PMOS pair at top. This CMOS pair is used to achieve more positive gain for same power consumption. The CMOS cross coupled topology without or with tail are show in

Page | 507

figure 3.1(a) and figure 3.1(b). The total negative resistance of CMOS pair which include parallel combination of NMOS pair's negative resistance  $R_{inn}$  and PMOS pair's negative resistance  $R_{inp}$  as show in figure 3.1(c). It express as

$$R_{negative} = R_{inn} / / R_{inp} = \frac{z}{g_{mn} + g_{mp}}$$

It is know that phase noise is contributed by flicker noise of active devices. This active devices up convert this flicker noise in the phase noise region with slop -30dB/decade so called  $1/f^3$  phase noise region. This noise can be minimized by equating rising and falling time of oscillation waveform. This condition can be achieved when NMOS and PMOS device has equal transconductance is express as:

# $g_{mn} = g_{mp}$

In this condition better rise and fall time symmetry achieve which reduces the up conversion of 1/f transistor noise. Therefore CMOS structure attains a smaller  $1/f^3$  noise corner in noise characteristic which exist in NMOS cross coupled differential topology.

There are another advantage of CMOS cross coupled differential topology that it consume less current because for given biased current both NMOS and PMOS attain negative resistance so it is possible to compensate loss in LC tank with lower biased current than in NMOS only structure. The important advantage of CMOS cross coupled differential topology is that CMOS structure attains peak differential output amplitude twice as high NMOS only structure.

www.ijsart.com

#### (c)

# Figure 3.1 (a) (a), (b) CMOS cross-coupled differential oscillator without and with tail current source and (c) calculation of total negative resistance of CMOS differential topology.

The CMOS cross coupled differential topology also experience drawbacks over cross coupled differential topology. The first disadvantage of CMOS cross coupled topology is that this topology offers higher parasitic capacitance which mean lower tuning range. This because the parasitic capacitance contributed by PMOS pair may as high as five times the parasitic capacitance contributed by NMOS pair of cross coupled differential topology.

Second disadvantage is arises when tail current source incorporated with CMOS cross coupled differential topology as show in figure.

Another thing is bulk driven concept. The principle of the bulk-driven technique is that the input is given on the body that is less than the threshold voltage and a voltage is being set on the gate terminal so as to form a channel. The thickness of the depletion zone i.e. the conduction channel is affected by the bulk voltage. A bulk-driven symmetrical OTA operating in weak inversion can result in both reduced power consumption and high linearity.

Bulk-driven MOSFET was first adopted in [12]. While designing an OTA while adopting the bulk-driven technique, the most significant stage is the input stage. In this technique, a fixed voltage is associated with the gate terminal and the input is given into the bulk terminal. With the zerobias voltage on the bulk terminal, the transistors are in weak inversion. The two fundamental favorable circumstances of utilizing the bulk-driven system are that the bulk- driven differential sets in an OTA and incredibly enhances the transconductance and the threshold voltage of the transistor vanishes and both negative and positive bias voltages (Vbs) are conceivable. Whereas there are a couple ISSN [ONLINE]: 2395-1052

of downsides to this technique when contrasted with the gate driven method, for example, little transconductance due to the less input capacitance of the depletion layer and larger parasitic capacitance to the mass which diminishes the fT. Due to the smaller transconductane, the device will have high input referred noise. The advantage of a Bulk-driven device over a gate-driven device is that the threshold voltage limitation disappears and both positive and negative bias voltages (Vbs) are possible. This is especially important in analog lowvoltage circuits where the dynamic range of the signal should be maximized with respect to the supply voltage in order to maximize the performance of the circuit.

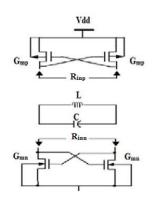

Finally compounded transistor pair technique is used. This technique increase output impedance and transconductance. Figure 3.2 shows compound transistor pair which is used in this project.

Figure 3.2 Compound transistor pair[23]

# **IV. DESIGN**

#### 4.1 Inductor Design

The inductor used in this thesis were realized in an iterative fashion for an intended use in cross-coupled CMOS LC oscillators. The primary objective in the design process was to design inductors to support the oscillator's operating frequency of RF band. A tank circuit with  $C_{max}/C_{min}$  is 0.94pF/0.46pF and L = 1 nH exhibits centre frequency for design is 6 GHz. These obtain centre frequency for design is different from theoretical frequency due to parasitic effect of MOS transistor.

#### 4.2 Varactor Design

The aim for varactor design is to achieve desired range of tuning frequency for LC tank. The tank circuit capacitance is associated with variable varactor capacitance and fixed parasitic capacitance related to inductor and amplifier which limit the tuning range. This PMOS capacitance is implemented by connecting two identical PMOS transistor in series which operate in inversion mode. The varactor has a maximum capacitance 0.94 pF and a minimum capacitance of 0.46 pF. It provides tuning range of 2.35GHz for frequency range 5 GHz-7.35GHz. The PMOS varactor has dimension width,(W) = 8 um, channel length, (L) = 200nm and number of multiplier, (M) = 50.

#### 4.3 L in parallel with C

Figure 5.1 shows the proposed design with high value capacitor is connected in parallel with the current source and shunts the second harmonic noises of the current to the ground. In addition, to provide high impedance and at the same time resonate the parasitic of the current source at the second harmonic (2fo) a source inductor is implemented connecting the current source with the cross-coupled transistors[22]. So, L is chosen as 1nH and C is calculated 0.7 pF on the basis of frequency 6 GHz.

# V. RESULTS & COMPARISION

## **5.1Tabulation of Parameters extracted**

CMOS LC VCO design has very low power consumption. The low value of power is obtained due to implementation of cross coupled pair of PMOS transistor in design of LC VCO. This design of CMOS LC VCO has very optimized tuning range. The two PMOS are connected back to back and biased in inversion mode in design. The results are summarized in Table 5.1.

Table 5.1 (A) Results of CMOS LC VCO. Simulation result S.No. Parameter Technology 45nm 1. Power 2. 3.9 Consumption(mW) Frequency(GHz) 5-7.35 থ Tuning Voltage(V) 4 0.0-1.2 Tuning Range (%) 39.2 5.

@1MHz

offset

-197 @1 MHz

118.84

# 5.2 Phase Noise & Figure of Merit(FOM)

Phase Noise(dBc/Hz)

FOM(dBc/Hz)

6.

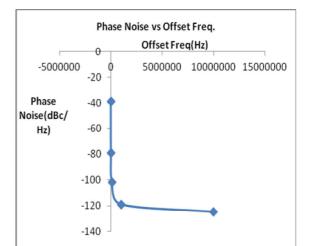

Fig. 5.1 shows that the phase noise at an offset of 1MHz is -118.84 dBc/Hz, respectively.

FOM of the proposed VCO is -197 dBc/Hz/ at 1 MHz offset from 6 GHz operating frequency that is better than other reported works.

Fig.5.1 Relationship between Phase Noise and Offset freq.

#### VI. CONCLUSION

Bulk bias LC VCO is shown which is working on 45 nm technology and at 1.2 V supply. In this, a PMOS and a NMOS on both side is added in addition to conventional circuit. 0.1 V is applied at the body of NMOS transistor which reduce's the power consumption to 3.9 mW. This VCO generating frequency from 5 GHz to 7.35 GHz which makes this circuit good candidate for multistandard wireless communication protocol.

With this technique, -118.84 dBc/Hz of phase noise and FOM of -197 dBc/Hz is obtained.

## REFERENCES

- M. Moghavvemi and AliyarAttaran"Performance Review of High-Quality-Factor, Low-Noise, and Wideband Radio-Frequency LC-VCO for Wireless Communication [Application Notes]", Microwave Magazine, vol. 12, pp. 130-146, June 2011.

- [2] Mohammad Niaboli-Guilani, Dalenda Ben Issa, AbdennaceurKachouri and MounirSamet, "A Low Power Low Phase Noise CMOS Voltage Controlled Oscillator", in 17th International Conference Electronics, Circuits, and Systems (ICECS), pp. 422 - 425, Dec. 2010.

- OfirDegani, YosiShacham-Diamandand [3] Alex Katz. EranSocher, "А beyond 60GHz Cross-Coupled Fundamental VCO in 45nm CMOS", in IEEE International Conference on Microwaves, Communications, Antennas and Electronics Systems, pp. 1-5. Nov. 2009.

- [4] Cheol-Hoe Kim, Soo-Hwan Shin, and Hyung-JounYoo,"A Low Phase Noise and Low Power Series Coupled Quadrature VCO Using Reconfigurable LC Tank",in International Conference Radio and Wireless

Symposium, pp. 395 - 398, Jan. 2008.

- [5] Nabil Boughanmi, Dalenda ben issa. Abdennaceurkachouri andMounirsamet"High Q-VCO with Low phase noise for Communications applications", in the International, Design and Test of Integrated Systems in Nanoscale Technology, Conference, pp. 370- 373, 2007.

- [6] Albert Jerng and Charles G. Sodini, "The Impact of Device Type and Sizing on Phase Noise Mechanisms", IEEE journal Of Solid State Circuits, Vol. 40, February 2005.

- [7] Han-il Lee, Tae-young Choi, SaeedMohammadi and Linda P.B. Katehi, "An Extremely Low Power 2 GHz CMOS LC VCO for Wireless Communication Applications", The European Conference on Wireless Technology, pp. 31-34, Oct. 2005.

- [8] Jie Long and Robert J. Weber, "A 2.4GHz Low-Power Low-Phase-Noise CMOS VCO Using Spiral Inductors and Junction Varactors", in Proceedings of the 2004 International Symposium on Circuits and Systems, Vol.4, pp. 545-548, 23-26 May 2004.

- [9] S. Levantino, C. Samori, A. Bonfanti, S.L.J. Gierkink and A.L. Lacaitai, "Frequency dependence on bias current in 5 GHz CMOS VCOs: impact on tuning range and flicker noise up conversion", IEEE J. of Solid-State Circuits, vol. 37, pp. 1003-1011, Aug. 2002.

- [10] BehzadRazavi, Design of Analog CMOS Integrated Circuits, Tata McGraw hill ed., 2002.

- [11] JakubKucera and Bernd-Ulrich Klepser, "3.6 GHz VCOs for multi-band GSM transceivers", in Proceedings of the 27th European Solid-State Circuits Conference, pp. 325-328, 18-20 September 2001.

- [12] A. Hajimiri and T. H. Lee, "Jitter and Phase noise in ring oscillators", IEEE J. Solid State Circuits, 34(6):790-804, June 1999.

- [13] Ali Hajimiri and Thomas H. Lee, "Phase Noise in CMOS Differential LC Oscillators", 1998 Symposium onVLSI Circuits-Digest of Technical Papers, pp. 48-51, Jun. 1998.

- [14] Maria del Mar Hershenson, Ali Hajimiri, Sunderarajan S. Mohana, Stephen P. Boyd and Thomas H. Lee, "Design and optimization of LC oscillators",1999 IEEE/ACM International Conference on Computer-Aided Design, pp. 65-69 Nov. 1990.

- [15] Dixit, M., Shrivastava, S. C., & Dixit, P. (2015). A 5–5.47 GHz LC-VCO using varactor configuration in 0.18 um CMOS technology.In 2015 2nd international conference on signal processing and integrated networks (SPIN), Feb, pp. 887–890.

- [16] Ji, X., Xia, X., He, L., & Guo, Y. (2017). Self-biased CMOS LCVCO based on trans-conductance linearisation technique. Electronics Letters, 53(22), 1460–1462.

- [17] Sadhu, B., Kim, J., & Harjani, R. (2009). A CMOS 3.3-

8.4 GHz wide tuning range, low phase noise LC VCO. In Custom integrated circuits conference, CICC'09. IEEE. pp. 559–562.

- [18] Hsu, M.-T., Chen, P.-H., & Lee, Y.-Y. (2014). Design of 5 GHz low-power CMOS LC VCO based on complementary crosscoupled topology with modified tail current-shaping technique. International Journal of Microwave and Wireless Technologies,6(6), 573–580.

- [19] Zhou, J., Li, W., Huang, D., Lian, C., Li, N., Ren, J., et al. (2013).A 0.4–6-GHz frequency synthesizer using dualmode VCO for software-defined radio. IEEE Transactions on Microwave Theory and Techniques, 61(2), 848–859.

- [20] Xiangning Fan, Li Tang, Xiaoming Si, and Zaijun Hua,

"Design of a Broadband vco for WSN Applications," IEEE International Conference on Microwaves, Communications, Antennas and Electronic Systems (COMCAS 2015),2-4 November 2015.

- [21] Mehrabian, M., Nabavi, A., & Rashidi, N. (2008). A 4-7 GHz ultra wideband VCO with tunable active inductor. IEEE international conference on ultra-wideband, 2008. ICUWB 2008, Vol. 2. IEEE, pp. 21–24.

- [22] Hegazi, E., Sjoland, H., & Abidi, A. A. (2001). A filtering technique to lower LC oscillator phase noise. IEEE Journal of Solid-State Circuits, 36(12), 1921–1930.

- [23] Mohammad Taherzadeh-Sani and Anas A. Hamoui, "A 1-V Process-Insensitive Current-Scalable Two-Stage Opamp With Enhanced DC Gain and Settling Behavior in 65-nm Digital CMOS," IEEE Journal of Solid-State Circuits, Vol. 46, no. 3,pp.660-668, March 2011.

- [24] Siddharth Bhat, Shubham Choudhary and J. Selvakumar, " Design of Low Voltage CMOS OTA Using Bulk-Driven Technique," Indian Journal of Science and Technology, Vol 9(19), pp.1-6, May 2016.

- [25] Jang, S.-L., et al. (2017). Dual-resonance concurrent oscillator.Microelectronics Reliability.

- [26] Wang, W., Li, W., Li, N., & Ren, J. (2014). An 8 to 9 GHz LCVCO and harmonic-suppressed CML divider with low supply voltage for FMCW synthesizer. In 2014 12th IEEE international conference on solid-state and integrated circuit technology (ICSICT). IEEE, pp. 1–3.

- [27] Elbadry, M., Kalia, S., & Harjani, R. (2014). A 52% tuning range QVCO with a reduced noise coupling scheme and a minimum FoMT of 196 dBc/Hz. IEEE proceedings of the custom integrated circuits conference (CICC), pp. 1–4,2014.

- [28] Bevilacqua, A., Pavan, F. P., Sandner, C., Gerosa, A., & Neviani, A. (2007). Transformer-based dual-mode voltage-controlled oscillators. IEEE Transactions on Circuits and Systems II:Express Briefs, 54(4), 293–297.

- [29] Abdelhamid Aitoumeri, Abdelmalik Bouyahyaoui and Mustapha Alami, "5.18–7.42 GHz LC-VCO in subthreshold regime with low power low phase noise and

immunity to PVT variations in 130 nm CMOS technology," Analog Integrated Circuits and Signal Processing, Feb. 2018.