# Power Qualities Issues And Its Mitigation Techniques

Prakash Kumawat<sup>1</sup>, Mr. Sunil Kumar<sup>2</sup>

<sup>1</sup>Dept of EE

<sup>2</sup>Assistant professor, Dept of EE

1,2 Sobhasaria group of institutions sikar

Abstract- The most noticeable topic for electrical engineering is power quality in recent year. Power quality problem is an occurrence manifested as a nonstandard voltage, current or frequency. Utility distribution networks, sensitive industrial load and critical commercial operation suffer from various types of outages and service interruption can cost significant financial losses. One of the major problems dealt here is the voltage sag.

With the fast development in power electronics technology have made it possible to mitigate power quality problems. This work concentrates on the power quality problem such as voltage sag. Many of the devices such as STATCOM, tap changing transformer, UPFC and DVR are available to mitigate voltage sag problems. Among these, dynamic voltage restorer can provide the most commercial solution to mitigate voltage sag by injecting voltage as well as power in to the system.

Dynamic Voltage Restorer is a series connected power electronics based device that can quickly mitigate the voltage sag in the system and restore the load voltage to the pre-fault value.

This thesis first gives an introduction to relevant power quality problems for a DVR and power electronics controllers for voltage sag mitigation. Thereafter the operation and elements in DVR is described. In this thesis proposed utilizes the error signal to control the triggering of the switches of an inverter using Sinusoidal Pulse Width Modulation (SPWM) technique.

Modeling and simulation of proposed DVR is implemented in MATLAB SIMULINK

## I. INTRODUCTION

"Reliability" is a key word for utilities and their customers in general, and it is crucial to companies operating in a highly competitive business environment, because it affects profitability, which definitely is a driving force in the industry. Although electrical transmission and distribution systems have reached a very high level of reliability, disturbances cannot be totally avoided. Any disturbances to

voltage waveform can cause problems related with the operation of electrical and electronic devices[1]. Users need constant sine wave shape, constant frequency and symmetrical voltage with a constant rms value to continue the production[2]. This increasing interest to improve efficiency and eliminate variations in the industry has resulted more complex instruments sensitive to voltage disturbances such as voltage sag, voltage swell, interruption, phase shift and harmonic. Voltage sag is considered the most severe since the sensitive loads are very susceptible to temporary changes in the voltage. In some cases, these disturbances can lead to a complete shutdown of an entire production line, in particular at high tech industries like semiconductor plants, with severe economic consequences to the affected enterprise[3].

ISSN [ONLINE]: 2395-1052

The DVR is a power quality device, which can protect these industries against the bulk of these disturbances, i.e. voltage sags and swells related to remote system faults[2,4]. A DVR compensates for these voltage excursions, provided that the supply grid does not get disconnected entirely through breaker trips. Modern pulse-width modulated (PWM) inverters capable of generating accurate high quality voltage waveforms form the power electronic heart of the new Custom Power devices like DVR. Because the performance of the overall control system largely depends on the quality of the applied control strategy, a high performance controller with fast transient response and good steady state characteristics is required[5]. The main considerations for the control system of a DVR include: sag detection, voltage reference generation and transient and steady-state control of the injected voltage[6].

The typical power quality disturbances are voltage sags, voltage swells, interruptions, phase shifts, harmonics and transients. Among the disturbances, voltage sag is considered the most severe since the sensitive loads are very susceptible to temporary changes in the voltage[7].

Page | 775 www.ijsart.com

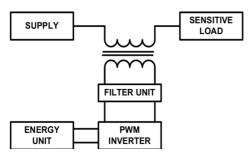

Figure 1 Typical applications of DVR and its output.

The wide area solution is required to mitigate voltage sags and improve power quality. One new approach is using a DVR . The basic operation principle is detecting the voltage sag and injecting the missing voltage in series to the bus as shown in Fig.1. DVR has become a cost effective solution for the protection of sensitive loads from voltage sags[8]. The DVR is fast, flexible and efficient solution to voltage sag problems. DVR consists of energy storage unit, PWM inverter, and filter and injection transformer as shown in Fig.4.1

### **Futures of DVR:**

- Lower cost, smaller size, and its fast dynamic response to the disturbance.

- Ability to control active power flow.

- Higher energy capacity and lower costs compared to the SMES device.

- less maintenance required. UPS is costly; it also requires a high level of maintenance because batteries leak and have to be replaced as often as every five years.

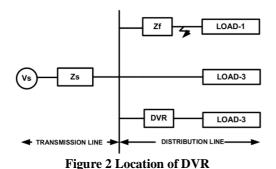

## Location of DVR:

DVR is connected in the utility primary distribution feeder. This location of DVR mitigates the certain group of customer by faults on the adjacent feeder as shown in Fig 2[9]. The point of common coupling (PCC) feds the load and the fault. The voltage sag in the system is calculated by using voltage divider rule.

The insertion of a DVR at the low voltage four-wire 440 V level is illustrated in Fig. 4.2. The increase in impedance by insertion of a small rated DVR can be significant for the load to be protected from voltage dips. Thereby, the per cent change in the impedance ( $Z_{increase}$ , %) in can be increased by several hundred per cent[10].

Inserting a DVR at LV-level has certain advantages:

- The DVR can be targeted more specifically at voltage dip sensitive loads.

- a majority of electric customers have only access to the LV-level and the DVR can both be placed by the customer at the customer domain or by the utility at the utility domain.

- The short-circuit level is significantly decreased by the distribution transformer and the DVR is easier to protect.

The disadvantages with a LV solution are:

- The impedance increase after the insertion of the DVR for the protected load can be large, which may influence the site short circuit level and protection[6,8]. An increased load voltage distortion and load voltage variation can be expected, which may be caused by non-linear and time varying load currents.

- Voltage dips with a zero sequence voltage component can appear and in order to be able to compensate loads connected between phase and neutral adequate, the DVR hardware and control should be able to generate positive, negative and zero sequence voltages[11].

## Working of DVR:

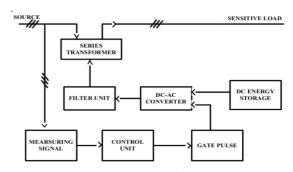

Figure 3 Function blocks of designed DVR

Among the voltage transients (sags, swells, harmonics...), the voltage sags are the most severe disturbance. The users may improve end-use devices or use

Page | 776 www.ijsart.com

protection devices to reduce the number of voltage sags. But overall solution to mitigate the voltage sags and recovering the load voltage to the pre-fault value is using a Dynamic Voltage Restorer (DVR)[12]. It is a solid state DC to AC switching power electronic converter that injects three single-phase AC voltages in series between the feeder and sensitive load. Using a DVR is more reliable and quick solution to maintain with a clean supply of electricity for customers. But standby losses, equipment costs and required large investigation for design are the main drawbacks of DVR. The PWM inverter unit produces required missing voltage by evaluating the control unit signals and this compensating voltage is inserted to the system by injection transformers[13].

## Control strategy of DVR

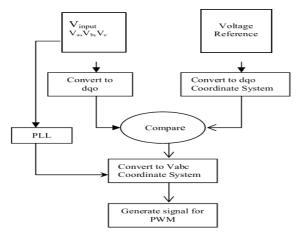

Figure-4 Flowchart of feed forward control techniquefor DVR based on dqo transformation.

The basic functions of a controller i n a DVR are the detection of voltage sag/swell events in the system; computation of the correcting voltage, generation of trigger pulses to theSinusoidal PWM based DC-AC inverter, correction of any anomalies in the series voltage Injection and terminationofthe trigger pulses when the event has passed. The controller may also be used to shift the DC-AC inverter into rectifier mode to charge the capacitors in the DC energy link in the absence of voltagesags/swells[14]. The dqo transformation or Park's transformation is used to control of DVR.The dqomethod gives the sag depth and phase shift information with start and end times. The Quantities are expressed as the instantaneous space vectors. Firstly convert the voltage from abc reference frame to dqoreference. For simplicity zero phase sequence components is ignored.

Figure-3.10 illustrates a flow chart of the feed forward dqo transformation for voltage sags/swells detection. The detection is carried out in each of the three phases.

The control i s based on the comparison of a voltage reference and the measured terminal voltage ( $V_a$ ,  $V_b$ ,  $V_c$ ). The voltage sags is detected when the supply drops below 90% of the reference value whereas voltage swells is detected when supply voltage increases up to 25% of the reference value[15]. The error signal is used as a modulation signal that allows generating a commutation pattern—for the power switches (IGBT's)—constituting—the voltage sourceconverter. The commutation pattern is generated by means of the sinusoidal pulse width modulation technique (SPWM); voltages are controlled through the modulation.

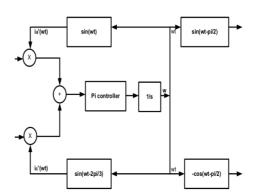

The block diagram of the phase locked loop (PLL) is illustrated in Figure-4.10 The PLL circuit is used to generate a unit sinusoidal wave in phase with mains voltage.

Figure 5 Block diagram of PLL

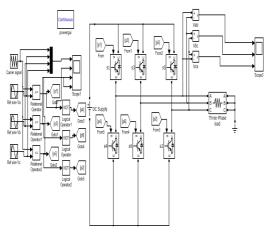

## II. SIMULATION AND RESULTS

### 2.1 Simulation for Sag and Swell without DVR:

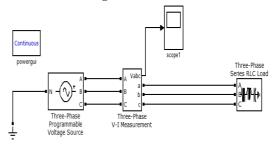

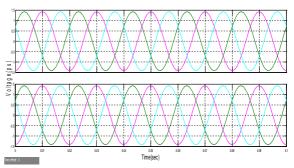

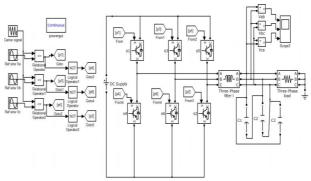

Figure 6: simulation circuit for voltage sag and swell without DVR

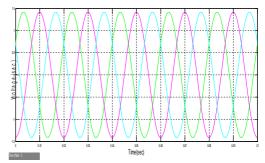

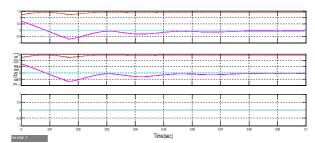

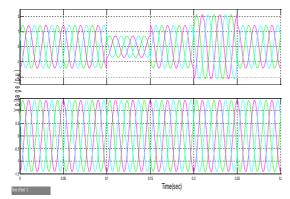

The system consists of voltage of 1 pu, 50 Hz source with 10kw 3-phase RLC load shown in fig 5.1. voltage sag is occurred at 0.5 sec to 1 sec of .5 pu and voltage swell occurred of 0.5 pu for 0.2 sec to .25 sec. Fig: 5.2 shows three phase voltage waveform under fault condition

Page | 777 www.ijsart.com

without DVR. As shown fig 5.1, sag occurs at 0.1 sec to 0.15 sec. Now the function of DVR would be to inject acompensating voltage, which would result in fairly constant voltage across the load terminal. With the use of the fast acting power electronics converters, DVR is capable to inject voltage for such a small duration of few cycles. The simulation parameters given in following table

| Supply Source     | 3-Ф, 1 рuV 50 Hz |

|-------------------|------------------|

| Load              | 10kW, 100Var     |

| Filter            | L=20mH, C=30µF   |

| DC Voltage Source | 600♥             |

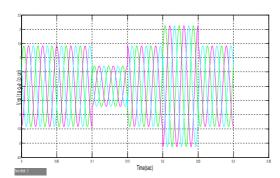

Figure 6: simulation result for voltage sag and swell without DVR

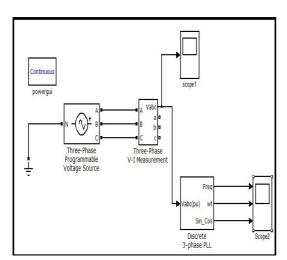

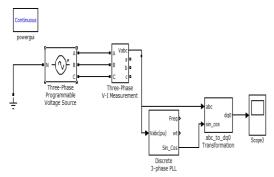

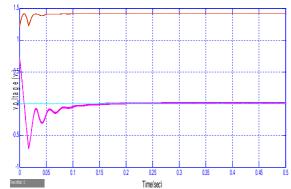

## 2.2 Simulation of system with PLL circuit:

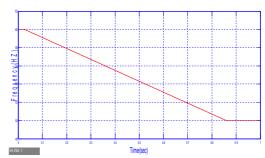

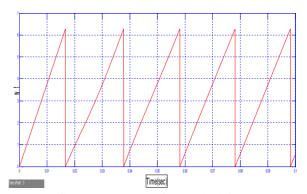

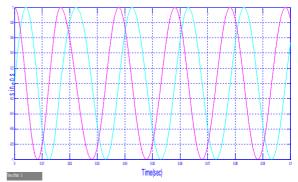

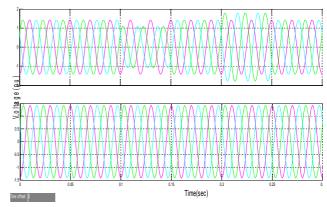

Fig 5.3 shows the simulation of system with PLL circuit which gives the output of frequency wt, and sin\_cos function which is as shown in fig. 2.4, fig,2.5 and fig 2.6 respectively,

Figure 7: Simulation of system with PLL circuit

Figure 8: Simulation result of voltage for system with PLL circuit

Figure 9: Simulation result of Frequency for system with PLL circuit

Figure 10: Simulation result of angle (wt) for system with PLL circuit

Figure 11: Simulation result of function sin\_cos for system with PLL circuit

Page | 778 www.ijsart.com

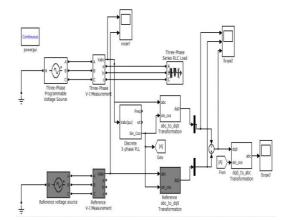

# Simulation for system with PLL circuit and abc to dq0 Block

Fig 2.8 shows the simulation of system with abc to dq0 transformation block which convert voltage waveform into dq0 form as shown in fig 5.9

Figure 12: Simulation for system with PLL circuitand abc to dq0 Block

Figure 13: Simulation result of voltage in dq0 for system with PLL circuit and abc to dq0 block

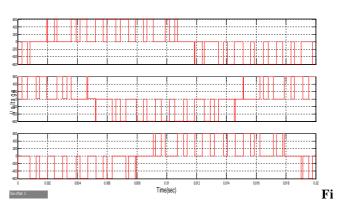

## Simulation for system with error signal generated

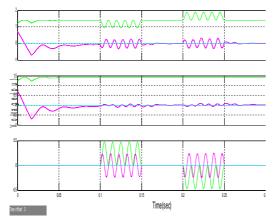

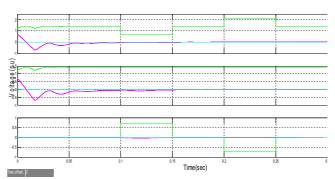

Fig 2.9 shows the simulation of comparison of reference voltage and supply voltage fig 5.10 shows the supply voltage and reference voltage in steady state condition.

Figure 14 Simulation for system with error signal generated

Figure 15: Simulation result of supply voltage and reference voltage

Figure 16: Simulation result of supply voltage and reference voltage and error signal in dq0

Figure 17: Simulation result of supply voltage and reference voltage in the event of sag and swell in one phase

Page | 779 www.ijsart.com

Figure 18: Simulation result of supply voltage and reference voltage and error signal in dq0 in the event of sag and swell in one phase

Figure 19: Simulation result of error signal in abc in the event of sag and swell in one phase

Figure 20: Simulation result of supply voltage and reference voltage in the event of sag and swell in all phases

Figure 21: Simulation result of supply voltage and reference voltage and error signal in dq0 in the event of symmetrical sag and swell

Figure 22: Simulation result of error signal in abc in the event of symmetrical sag and swell

Fig 2.16,fig.2.17 and fig.2.18 shows the output of voltage,Simulation result of supply voltage and reference voltage and error signal in dq0 in the event of symmetrical sag and swell,Simulation result of error signal in abc in the event of symmetrical sag and swell respectively.

### simulation of SPWM based inverter

# **Generation of Gate pulse:**

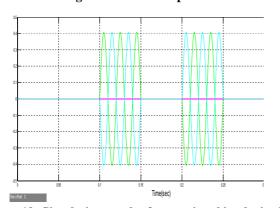

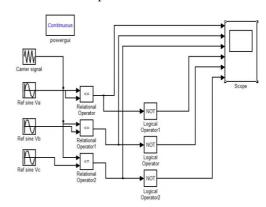

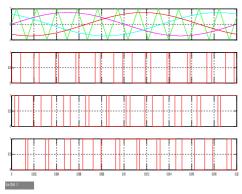

Fig. 2.19 shows the pulse generation circuit in which reference wave is compared with carrier wave.

Figure 23: Generation of Gate Pulse

Page | 780 www.ijsart.com

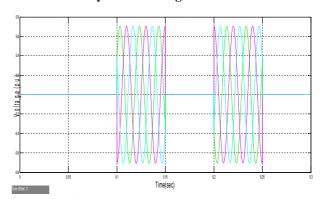

Figure 24: waveforms of Gate Pulse Generation

Fig 5.20 shows the phenomenon of pulse generation, when the reference wave magnitude is more than carrier wave the pulse is generated.

Figure 25: Gate Pulses

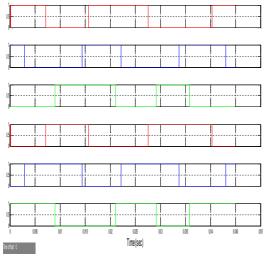

## 5.5.2 Generation of Gate pulse

Figure 26: SPWM based inverter Without Filter Circuit

Fig 2.22 shows the SPWM without Filter circuit the output waves contains harmonics as shown in fig.5.23

gure 27: SPWM based inverter Voltage waveforms

Without Filter Circuit

### 2.5.3 Simulation of SPWM inverter with filter circuit

Figure 28: SPWM based inverter With Filter Circuit

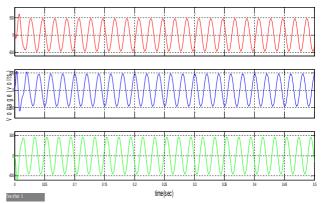

Fig 2.24 shows the simulation of SPWM inverter with Filter circuit so that the output voltage is purely sinusoidal as shown in fig, 2.25

Figure 2.25: SPWM based inverter Voltage waveforms

With Filter Circuit

Page | 781 www.ijsart.com

### ISSN [ONLINE]: 2395-1052

#### III. CONCLUSION

In this thesis the main objectives for the utilization of the studied equipment to mitigate the voltage sag and voltage swell. In order to protect critical loads from more sever fault in distribution network. The facility available in MATLAB/SIMULINK is used to carry out extensive simulation study.

Supply voltage is compared with reference voltage to get error signal which is given to the gate pulse generation circuit as a reference sine wave which is compared with carrier signal to get pulses for inverter.

PLL circuit is used to extract angle from supply voltage so that this circuit can be used at supply of any frequency so the error signal will be synchronised supply frequency.

### REFERENCES

- [1] Faris Hamoud, Mamadou Lamine Doumbia, Member, IEEE, "Voltage Sag and Swell Mitigation Using DSTATCOM in Renewable Energy Based Distributed Generation Systems" in IEEE transactions on 2017 Twelfth International Conference on Ecological Vehicles and Renewable Energies (EVER).

- [2] Kirti Mathuria, Arun Kumar Verma, Member, IEEE, Bhim Singh, Fellow, IEEE and G. Bhuvaneswari, Senior Member, IEEE Department of Electrical Engineering, Indian Institute of Technology Delhi, "Modified Series Compensation for Voltage Sag /Swell Mitigation" in IEEE transations.

- [3] Kirti Mathuria, Arun Kumar Verma, Bhim Singh and G. BhuvaneswariIndian Institute of Technology Delhi, New Delhi-110016, India. "Single-Phase Series Active Compensator Integrated with a Rectifier for Voltage Sags, Swells and Harmonics Mitigation" in IEEE transations.

- [4] Amit Kumarl, Nidhi Singh Pal2 and M.A. Ansari3, " Mitigation of voltage sag swell and harmonics using self supported DVR", 1st IEEE International Conference on Power Electronics. Intelligent Control and Energy Systems (ICPEICES-2016)

- [5] C.E. Thenmozhi, C.Gopinath, R.Ramesh pG Student, AP (Sel.Grade), Dept. of EEE, Easwari Engineering College, Chennai, Tamilnadu, India. Research Scholar, Associate Professor3, Dept.of EEE, College of Engineering, Anna University, Chennai. "A Novel Method For Voltage Sag / Swell Compensation Using Dynamic Voltage Restorer". IEEE- International Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31,2012.

- [6] Ravilla Madhusudan, Student Member, IEEE, G. Ramamohan Rao IpQ Scholar, Department of Electrical and Electronics Engineering Associate Professor, Department of Electrical and Electronics Engineering Sir C R Reddy College of Engineering, Eluru, India, "Modeling and Simulation of a Distribution STATCOM (D-STATCOM) for Power Quality Problems-Voltage Sag and Swell Based on Sinusoidal Pulse Width Modulation (SPWM)". IEEE- International Conference On Advances In Engineering, Science And Management (ICAESM 2012) March 30, 31,2012.

- [7] Ravilla Madhusudanl, Student Member, IEEE, G. Ramamohan Rao pG Scholar, Department of Electrical and Electronics Engineering Associate Professor, Department of Electrical and Electronics Engineering Sir C R Reddy College of Engineering, Eluru, India. "Modeling and Simulation of a Dynamic Voltage Restorer (DVR) for Power Quality Problems Voltage Sags and Swells". IEEE- International Conference On Advances In Engineering, Science And Management (ICAESM -2012) March 30, 31,2012 442.

- [8] Hafiz Furqan Ahmed, Honnyong Cha, Member IEEE, and Ashraf Ali Khan Kyungpook National University 80 Daehakro, Bukgu, 702-701 Daegu, Korea. "Design of Dynamic Voltage Restorer for Voltage Sag and Swell Compensation using High-Frequency-Isolated Direct AC-AC Converter without Commutation Problem".

- [9] S. Masoud Barakati ECE Department, University of Sistan and Bluchestan, Zahedan, Iran, Arash Khoshkbar Sadigh EECS Department, University of Irvine, CA, 92617, USA, Ehsan Mokhtarpour ECE Department, University of Tabriz, Tabriz, Iran. "Voltage Sag and Swell Compensation with DVR Based on Asymmetrical Cascade Multicell Converter".

- [10] Soma Biswas, Swapan Kumar Goswami, Amitava Chatterjee Department of Electrical Engineering, JIS College of Engineering, Kalyani, West Bengal 741235, India Department of Electrical Engineering, Jadavpur University, Kolkata, West Bengal 700032, India. "Optimal distributed generation placement in shunt capacitor compensated distribution systems considering voltage sag and harmonics distortions". Published in IET Generation, Transmission & Distribution Received on 19th June 2013 Revised on 1st November 2013 Accepted on 14th November 2013.

- [11] Marcelo C. Cavalcanti, Leonardo R. Limongi, Marcio D. B. Gomes, Gustavo M. S. Azevedo, Member, IEEE, and Luiz G. B. Genu. "Eight-Switch Power Conditioner for Current Harmonic Compensation and Voltage Sag Mitigation". IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS.

Page | 782 www.ijsart.com

ISSN [ONLINE]: 2395-1052

[12] Norbert EDOMAH Industrial Co-ordinator, Institute for Industrial Technology (liT), Lagos, Nigeria. "EFFECTS OF VOLTAGE SAGS, SWELL AND OTHER DISTURBANCES ON ELECTRICAL EQUIPMENT AND THEIR ECONOMIC IMPLICATIONS". 20th International Conference on Electricity Distribution Prague, 8-11 June 2009.

Page | 783 www.ijsart.com