# High Speed Multiplication using Ancient Mathematics – Urdhwa Tiryagbhayam

### RanjanaKumari<sup>1</sup>, Prof. Ashish Maske<sup>2</sup>

Department of E&TC

<sup>1</sup>PG Students, DPCOE Pune, India

<sup>2</sup>HOD, DPCOE Pune, India

Abstract-The most important fundamental cell in any processor is multiplier which forms the basis of most of the computations in the technical formulas. The multiplier based on conventional method takes long time for completing the multiplication as compared to the multipliers using vedic mathematics. Huge Arithmetic Multiplication functions are currently used in many Digital Signal Processing (DSP) applications such as convolution, Fast Fourier Transform (FFT), filtering and in microprocessors in its arithmetic and logic unit. Since multiplication dominates the execution time of the processors algorithms, which makes for the great need of high speed multiplier. Multiplication is an important and factor in evaluating the processing of instructions processed per unit in all types of processors. The demand for high speed processing has been growing as a result of developing computer and signal processing applications. This leads for an efficient throughput processor that is required for getting the desired performance in most of the Digital signal processing applications. So, arithmetic operations in the processors require multiplication which makes development of fast multiplier circuit; which has been a subject of interest over decades. Multiplier based on Vedic mathematics calculates the required multiplication in less time thereby consuming less Gates, LUTs & IOBs. Employing this technique in the computation algorithms will reduce the complexity, execution time, power etc.

*Keywords*-Urdhwa Tiryagbhayam, Reversible Gate, Vedic Mathematics, 32x32 Vedic Multiplier, Xilinx

#### I. INTRODUCTION

#### ANCIENT VEDIC MATHEMATICS

The word 'Vedic' means the store-house of all knowledge derived from the word 'veda'. It was introduced by Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaja as Vedic Mathematics. Vedic mathematics consists of 16 Vedic Sutras.

#### **VEDIC SUTRAS**

Vedic mathematics consisting of 16 Sutras deals with various branches of mathematics like arithmetic, algebra, geometry etc. Below are the 16 Sutras definitions:-

- 1) (Anurupye) Shunyamanyat The work of it is if the one is in ratio; then other is zero

- 2) Chalana-Kalanabyham It means differences and similarities.

- 3) Ekadhikina Purvena It means by one more than the previous one

- 4) Ekanyunena Purvena It means by one less than the previous one

- 5) Gunakasamuchyah It means the factors of the sum is equal to the sum of the factors

- 6) Gunitasamuchyah It means the product of the sum is equal to the sum of the product

- 7) Nikhilam Navatashcaramam Dashatah It means all from 9 and the last from 10

- 8) Paraavartya Yojayet It means Transpose and adjust.

- 9) Puranapuranabyham It means by the completion or noncompletion

- 10) Sankalana-vyavakalanabhyam It means by addition and by subtraction

- 11) Shesanyankena Charamena It means the remainders by the last digit

- 12) Shunyam Saamyasamuccaye It means when the sum is the same that sum is zero

- 13) Sopaantyadvayamantyam It means the ultimate and twice the penultimate

- 14) Urdhva-tiryakbyham It means Vertically and crosswise

- 15) Vyashtisamanstih It means Part and Whole

- 16) Yaavadunam It means whatever the extent of its Deficiency

## II. URDHVA-TIRYAKBYHAM - VERTICAL & CROSSWISE

The working of this multiplier is based on an algorithm Urdhva Tiryakbhyam (Vertical & Crosswise) of ancient Indian Vedic Mathematics. Urdhva Tiryakbhyam Sutra is a common multiplication formula which is applicable to all cases of multiplication. It's literal meaning is "Vertically and crosswise". It is based on the principle through

Page | 946 www.ijsart.com

which the generation of all partial products can be done with the concurrent addition of these partial products. The generation of partial products and their summation is obtained using Urdhava Tiryakbhyam explained in figure. The generalized form of the algorithm can be for n x n bit number. In this the partial products and their sums are calculated in parallel. Apart from it the multiplier is independent of the clock frequency of the processor. Therefore the multiplier will require the same amount of time to calculate the product and all the partial products and hence it is independent of the clock frequency. Therefore it can be said that the advantage of vedic multiplier is that that it reduces the need of microprocessors to operate at increasingly high clock frequencies. While a higher clock frequency generally results in increased processing power, its disadvantage is that it also increases power dissipation which results in higher device operating temperatures. By using the Vedic multiplier, microprocessors the designers can easily find a way around the problems to avoid fatal device failures.

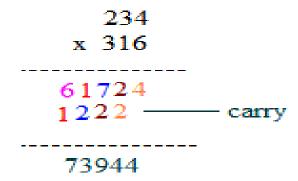

#### **MULTIPLICATION OF 3 DIGIT NUMBER 234\*316**

Urdhwa-Tiryagbhayam is the general formula applicable to all cases of multiplication. It means "Vertically and Crosswise."

- 1) Step 1 4\*6 = 24: [ 2 carried over digit placed below the 2nd digit]

- 2) Step 2 (3\*6)+(4\*1)=18+4=22: [ 2 carried over digit placed below the 3rd digit]

- 3) Step 3 (2\*6)+(3\*1)+(4\*3)= 12+3+12= 27: [ 2 carried over digit placed below the 4th digit]

- 4) Step 4- (2\*1)+(3\*3)=2+9=11: [ 1 carried over digit placed below the 5th digit]

- 5) Step 5 2\*3 = 6

- 6) Respective digits are added at the end. All the carries are added to produce the final answer: 73944

Figure 1:- Vedic Multiplication Example of 234\*316

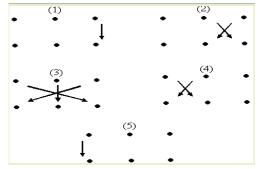

Figure 2:- General Rule for 3\*3 multiplication

#### III. ALGORITHM FOR VEDIC MULTIPLIER

Vedic Mathematics works on the 16 algorithms or sutras developed and derived from ancient Vedic texts. This particular method for fast multipliers used in digital image and signal processing techniques is named Urdhva Tiryakbhyam is more efficient and which consume less time and improves the speed and performance. This method performs multiplication in crosswise and vertically manner it makes all the numeric computations faster by generating partial product and sum in single iteration[1][2][3][4][5]. The Vedic multiplier calculates faster than the conventional multipliers. This gives a scheme for hierarchical multiplier design. The design is faster, consumes smaller area and has less power consumption as compared to the conventional multipliers.

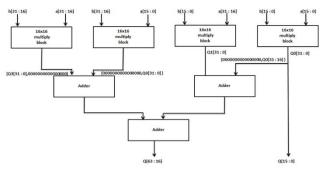

Figure 3: Block diagram of 32x32 UT Multiplier

Page | 947 www.ijsart.com

#### IV. PERFORMANCE ANALYSIS

The conventional multiplier requires more gates and so the processor using simple conventional multipliers speed becomes slow. The Table 1 and Table 2 gives the summary of the maximum path delay and number of Slices, LUTs and IOBs for both conventional multiplier and Reversible Gates [vedic maths] multipliers. The tables clearly shows that reversible gates are more efficient than conventional multiplier as uses less number of LUTs, Slices, IOBs; thereby making the processor speed fast using reversible gates [vedic math's].

Table 1: Comparison of speed using various multipliers

| Technology used                         | Maximum Path |  |  |  |

|-----------------------------------------|--------------|--|--|--|

|                                         | Delay        |  |  |  |

| 4x4 conventional multiplier             | 13.201 ns    |  |  |  |

| 4x4 multiplier using reversible gates   | 12.972 ns    |  |  |  |

| 8x8 conventional multiplier             | 26.177 ns    |  |  |  |

| 8x8 multiplier using reversible gates   | 24.484 ns    |  |  |  |

| 16x16 conventional multiplier           | 45.183 ns    |  |  |  |

| 16x16multiplier using reversible gates  | 40.214 ns    |  |  |  |

| 32x32 multiplier using reversible gates | 38.874 ns    |  |  |  |

Table 2: 32x32 multiplier using reversible gates [vedic maths]

| Number of Slices:       | 2896 out of 5720 (50 %        |  |  |  |  |  |

|-------------------------|-------------------------------|--|--|--|--|--|

|                         | utilized)                     |  |  |  |  |  |

| Number of LUTs FF pairs | 2896 out of 2896 (100%        |  |  |  |  |  |

| Used:                   | utilized)                     |  |  |  |  |  |

| Number of bonded IOBs:  | 128out of 102 (125% utilized) |  |  |  |  |  |

|                         |                               |  |  |  |  |  |

#### **OUTPUTS OF VEDIC MULTIPLIERS**

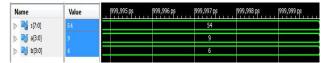

Figure 4:- Output of 4x4 Vedic Multiplier

| Name        | Value | 999,995 ps | 999,996 ps | 999,997 ps | 1999,998 ps | 999,999 ps |

|-------------|-------|------------|------------|------------|-------------|------------|

| ⊳ 💐 s[15:0] | 1500  |            |            | 1500       |             |            |

| ⊳ 😽 a[7:0]  | 30    |            |            | 30         |             |            |

| ⊳ 😽 b[7:0]  | 50    |            |            | 50         |             |            |

Figure 5:- Output of 8x8 Vedic Multiplier

| Name        | Value  | 1999,995 ps | 1999,996 ps | 999,997 ps | 999,998 ps | 999,999 ps |

|-------------|--------|-------------|-------------|------------|------------|------------|

| ⊳ 😽 s[32:0] | 494000 |             |             | 494000     |            |            |

| a[15:0]     | 650    |             |             | 650        |            |            |

| ⊳ 😽 b[15:0] | 760    |             |             | 760        |            |            |

Figure 6:- Output of 16x16 Vedic Multiplier

| Name        | Value    | 999,995 ps | 1999,996 ps | 999,997 ps | 999,998 ps | 999,999 ps |

|-------------|----------|------------|-------------|------------|------------|------------|

| > 😽 s[63:0] | 73090875 |            |             | 73090875   |            |            |

| ⊳ 😽 a[31:0] | 7755     |            |             | 7755       |            |            |

| ⊳ 😽 b[31:0] | 9425     |            |             | 9425       |            |            |

Figure 7:- Output of 32x32 Vedic Multiplier

A high speed 4x4 vedic multiplier, 8x8 vedic multiplier, 16x16 vedic multiplier , 32x32 vedic multiplier was designed with below inputs and outputs.

#### V. CONCLUSION

Thus an efficient Vedic multiplier with high speed, low power and consuming little bit wide area was designed and implemented on device Spartan and simulated using ISE simulator. It was found that the multiplier based on vedic sutras had execution delay of almost half of that of binary multiplier.

#### REFERENCES

- [1] S.P.Pohokar, R.S.Sisal,K.M.Gaikwad, M.M.Patil, Rushikesh Borse, "Design and Implementation of 16 x 16 Multiplier Using Vedic Mathematics", 2015 International Conference on Industrial Instrumentation and Control (ICIC), College of Engineering Pune, India. May 28-30, 2015

- [2] Honey Durga Tiwari, Ganzorig Gankhuyag, Chan Mo Kim, Yong Beom Cho, "Multiplier design based on ancient Indian Vedic Mathematics", Dept. of Electronics Engineering, Konkuk University, Seoul, South Korea

- [3] Rakshith Saligram,Rakshith T.R, "Optimized Reversible Vedic Multipliers for High Speed Low Power Operations", Proceedings of 2013 IEEE Conference on Information and Communicatio Technologies (ICT 2013)

- [4] Akhalesh K. Itawadiya, Rajesh Mahle, Vivek Patel, Dadan Kumar,"Design a DSP Operations using Vedic Mathematics",International conference on Communication and Signal Processing, April 3-5,2013, India

- [5] Sudeep. M. C, Sharath Bimba. M, Mahendra Vucha, "Design and FPGA Implementation of High Speed Vedic Multiplier", International Journal of Computer Applications, Volume 90-No. 16, March 2014.

- [6] A.M.Raid, W.M.Khedr, El-dosuky, Wesam Ahmed, "Jpeg Image Compression using Discrete CosineTransform - A

Page | 948 www.ijsart.com

- Survey", International Journal of Computer Science & Engineering Survey (IJCSES) Vol.5, No.2, April 2014

- [7] Prakash Narchi, Siddalingesh S Kerur, Jayashree C Nidagundi, Harish M Kittur and Girish V A. Implementation of Vedic Multiplier for Digital Signal Processing. IJCA Proceedings on International Conference on VLSI, Communications and Instrumentation (ICVCI) (16):1–5, 2011. Published by Foundation of Computer Science

- [8] Sumit Vaidya and Deepak Dandekar. "Delay-power perfor-mance comparison of multipliers in VLSI circuit design". International Journal of Computer Networks & Communications (IJCNC), Vol.2, No.4, July 2010.

- [9] Dr. K.S. Gurumurthy, M.S Prahalad "Fast and Power Efficient 16×16 Array of Array Multiplier using Vedic Multiplication",

- [10] Anvesh kumar, Ashish Raman, R K Sarin, Arun Khosla "Small Area Reconfigurable FFT Design by Vedic Mathematics" in Proc IEEE ICAAE'10, Singapoure, vol 5, pp. 836-838, Feb. 2010

- [11] T. Stockhammer, M. M. Hannuksela, and T. Wiegand, —H.264/AVC in wireless environments, IEEE Trans. Circuits Syst.Video Technol., vol. 13, no. 7, pp. 657–673, Jul. 2003.

- [12] H. Schwarz, D. Marpe, and T. Wiegand, —Overview of the scalable video coding extension of the H.264/AVC standard, IEEE Trans. Circuits Syst. Video Technol., vol. 17, no. 9, pp. 1103–1120, Sep. 2007.

- [13] D. Marpe, H. Schwarz, and T. Wiegand, —Contextadaptive binary arithmetic coding in the H.264/AVC video compression standard, IEEE Trans. Circuits Syst. Video Technol., vol. 13, no. 7, pp. 620–636, Jul. 2003

- [14] Koren Israel, "Computer Arithmetic Algorithms," 2nd Ed, pp. 141-149, Universities Press, 2001.

- [15] J.Bhasker, "Verilog HDL Primer" BS P Publishers, 2003.

- [16] Ken Cabeen and Peter Gent "Image Compression and Discrete Cosine Transform

Page | 949 www.ijsart.com