# Design And Analysis of Performance Parameters of Adders

Prof. Dr. Sanjeev Sharma<sup>1</sup>, Rajashree Patil<sup>2</sup>, Prof. Mukesh Mahajan<sup>3</sup>

<sup>1,2,3</sup> Dept of Electronics and Telecommunication

<sup>1, 2, 3</sup> SITRC, Savitribai Phule Pune university

Abstract- Addition is the extensively used operation in every digital circuit. In every arithmetic operations adder is a primary building cube of digital system. Hence the digital system required the huge performance adder because the system performance is totally depends on adders design. In modern days, VLSI technique has seen large use of adders with a superior delay performance. This extract demonstrate a 4 bit adders - CLA (Carry Look Ahead Adder), CSA (Carry Save Adder), Carry Select Adder, RCA (Ripple Carry Adder). They has been designate as per cell usage, total hold-up time and apparatus utilization factor. The adders executed in Hardware Description Language using Xilinx Integrated Software Environment 9.2i Suite.

Keywords- RCA, CLA, CSA, Carry Select Adder.

## I. INTRODUCTION

In digital days like control systems, DSP circuits a binary addition is the important operation that continues to have a great role [1]. There are a distinct species of adders; every adder has certain performance and its own importance. Each adder is specify according to their application, purpose. So, the adders are crucial to have faster computation for great accuracy and small area consumption. Binary adders are the highly essential logic elements within a digital structure [1].

The interpretation of digital system design is determine by using the adder. Likewise, the binary adders are furthermost supportive in modified methods other than Arithmetic Logic Units (ALU), multipliers, dividers and memory addressing units and so on. Any developments in binary addition can result in a performance boost for any computing device and, thus enhance the efficiency of the whole system. Carry chain is the bigger drawback of binary addition. When increase in width of the input operands, then the distance of the carry chain also increases. That's why to enhanced the efficiency of carry-propagate adders, it is able to appreciate the carry chain, but didn't eliminate it. As a result, most digital designers come up building faster adders by optimizing computer architecture, because they tend to set the critical route for most computations. In this extract we mainly focus on finding a better adder for delay constraints, cell usage and apparatus utilization factor [1].

# **II. LITRATURE SURVEY**

Er. Aradhana Raju [1] has studied a technique for the improvement of the adder design with compact delay. The author was finding out the fastest adder between the numerous kind of binary and PPA's. The findings showed us that there is hardly any variance in delays when the lower bits are taken into account, but rise the number of bits there is a remarkable variance in delays. Again, greater the LUT's used greater will be the area expended. Author propose that no single type of architecture is the finest for all bit values, rather offer enough insights of which type of adders is the best for a definite bit value. Paper [2] is Arithmetic Multi Precision Adders. In this abstract numerous types of adders are taken for trial study of identical RCA, CSA, CLA, Carry Increment adder, Carry Select adder. This extract has been attained a various specifications like low latency, less power consumption and less gate count. Experimentally simulated and synthesized by using Xilinx ISE14.7, also tested in SPARTAN3E, XC3S1600E with speed of -5.

G. Karthik Reddy [3] proposed a relative study on least-power and high speed CSA. In this extract Power consumption, area and delay of diverse carry select adders for 8bit, 16bit, 32bit, 64bit have been studied. As in relative exploration has recently been done in Area, hold-up and power to all the Carry select adders. A new design structured on D latch has reduced area, power and delay as compared with the standard SQRT CSLA power, delay and area have been calculated by using SYNOPSYS Design Vision tool. The results exploration displays that the new D latch built carry save adder CSLA configuration is improved than the regular SQRT CSLA. Mr. Deepak Raj [4] is proposed a carry chain adders at greater bit widths (128 to 256 bits) has advanced performance when associated to serial adders. Because the adder is often the critical component which defines to a huge portion the cycle time and power dissipation for numerous digital signal processing and cryptographically implementations, it would be worthwhile for prospect FPGA designs to contain an enhanced carry route to allow tree

constructed adder designs to be optimized for place and routing. The area, delay and power exhausted by fully types of PPA are evaluated. The field of the adder designing is specific in terms of Look up tables (LUT) and Input Output bounds (IOB). The adder designs are implemented and hold-up time, power and area of entirely the adders are explored.

## **III. PROBLEM DEFINITION**

To simulate and analyze performance parameters of adders. The adders are realized in VHSIC Language (VHDL) based on Xilinx Integrated Software.

#### **IV. OBJECTIVE**

The main intent of design the numerous adders like Carry Select Adder, CLA, RCA and Carry Save Adder are the necessary part of ordinal circuit design. To analyze and compare various adders for least power and high speed operations and also to study the performance parameters of adders like region, delay and power distribution.

## V. PROPOSED SYSTEM

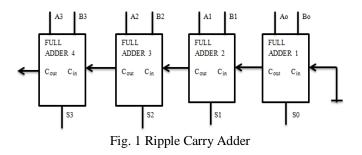

#### A. Ripple Carry Adder:

RCA sums 2 n-bit number plus carry input and gives n-bit sum and a carry output. The Vital process of Ripple Carry Adder is it ripple every carry output to carry input of following single bit addition. Every single bit addition is accomplished with full Adder operation (A, B, Cin) input and (Sum, Cout) output. 4-bit Ripple Carry Adder VHDL Code can be Certainly Assembled by Interface with 4 Full Adder. The below figure represent the 4-bit ripple adder. In the below figure, A, B 4-bit input, C0 is take in and S 4-bit output, C4 is take out. The left over C1, C2, C3 are intermediate Carry.

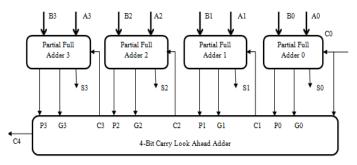

## B. Carry Look Ahead Adder:

This is supersonic adder equivalence with ripple carry adder. Intended for the determination of Propagation, Carry look adder build a part of Full Adder, Propagation and generation Carry block. It avoids Carry propagation done through every adder. To be able to put into practice Carry Look Ahead Adder, first implement Partial Adder and then logic by Propagation and generation Block. Partial Full Adder contain of inputs (A, B, Cin) and Outputs (S, P, G) where P is Transmit Output and G is Produce output[2].

Fig. 2 Carry Look Ahead Adder

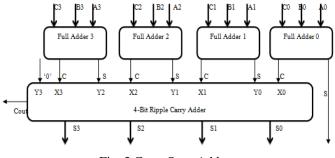

#### C. Carry Save Adder:

This adder used to accomplish 3 bit addition synchronously. Here 3 bit input (A, B, C) is administered and changed to 2 bit output (S, C) at first stage. At first stage outcome carry is not transmitted through addition operation. In order to create carry, realized ripple carry adder on step 2 for carry propagation [2].

Fig. 3 Carry Save Adder

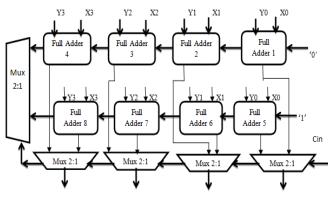

#### D. Carry Select Adder:

Carry Select Adder can be assembled by executing 2 stage Ripple Carry Adder besides multiplexer circuit. Carry Select Adder determine the sum and carry output to following level 1. ripple carry adder whereas carry input '0' and select Sum and carry output from level 2 ripple carry adder, when carry input '1'. For the determination of selecting sum and carry output, N+1 Multiplexer is implemented for N little bit Addition Operation.

Fig. 4 Carry Select Adder

# VI. SIMULATION RESULTS

A. Ripple Carry Adder:

Simulation of RCA adder

B. Carry Look Ahead Adder:

C. Carry Save Adder:

Fig. 7 Simulation of CSA adder

D. Carry Select Adder:

| Now:<br>1000 ns          |   | 100     | 200                  |         | 300     |  |

|--------------------------|---|---------|----------------------|---------|---------|--|

| ∎ <mark>51</mark> a[3:0] | 4 | 4'00000 | 4 <sup>1</sup> b1100 | 401111  | ¥b1110  |  |

| 🖬 😽 b[3:0]               | 4 | 4100000 | 461101               | 4'b1000 | 400101  |  |

| 🖬 😽 c[3:0]               | 4 | 400000  | 451110               | 4b1001  | 4'b0111 |  |

| 🖬 😽 s[4:0]               | 5 | 5100000 | 5'600111             | 5100000 | 5611010 |  |

| 👌 cout                   | 0 |         |                      |         |         |  |

Fig. 8 Simulation of carry select adder

# VII. RESULTS AND ANALYSIS

# Table 7.1 Delay Exploration

| Sr<br>N<br>0. | Adders                    | Logic<br>Delays (ns) | Route<br>Delay (ns) | Total<br>Delay<br>(ns) |

|---------------|---------------------------|----------------------|---------------------|------------------------|

| 1             | Ripple Carry<br>Adder     | 6.723                | 2.24                | 8.959                  |

| 2             | Carry Look<br>Ahead Adder | 6.723                | 2.197               | 8.920                  |

| 3             | Carry Save<br>Adder       | 6.72                 | 2.43                | 9.16                   |

| 4             | Carry Select<br>Adder     | 6.72                 | 2.24                | 8.96                   |

Table 7.2 Device Utilization Summary of various adders

| Sr.<br>No | Adders                    | Device Utilization Factor |                 |      |                 |  |

|-----------|---------------------------|---------------------------|-----------------|------|-----------------|--|

|           |                           | No. Of<br>Slices          | 4 mput<br>LUT's | IU's | Bonded<br>IOB's |  |

| 1         | Ripple Carry<br>Adder     | 4                         | 8               | 14   | 14              |  |

| 2         | Carry Look<br>Ahead Adder | 4                         | 8               | 14   | 14              |  |

| ز         | Carry Save<br>Adder       | 8                         | 14              | 18   | 18              |  |

| 4         | Carry Select<br>Adder     | 4                         | 8               | 14   | 14              |  |

Table 7.3 Cell Usage Summary of various adders

| Sr. | Adders                    | Cell Usage |       |      |      |

|-----|---------------------------|------------|-------|------|------|

| No. |                           | BEL's      | IOR.8 | IROF | OROF |

| 1   | Ripple Carry<br>Adder     | 8          | 14    | У    | C    |

| 2   | Carry Look<br>Ahead Adder | 8          | 14    | У    | C    |

| 5   | Carry Save Adder          | 14         | 18    | 12   | 0    |

| 4   | Carry Select<br>Adder     | 8          | 14    | У    | С    |

# VIII. CONCLUSION

This paper shows the strategy of various adders with reduced delay. The result is obtained for carry chain adders at lower bit rates regarding delay and area. After observing the result of comparisions, for 4 bit adders carry look ahead adder is better than others in concerning delay. Yet related to domain of ripple carry adder, carry select adder, carry save adder are superior than carry look ahead adder. In future this work can be extended by designing and simulating the adders with increased numeral of bits such as 8bits, 16bits, 32bits and 64 bits.

### REFERENCES

- Er. Aradhana Raju, Richi Patnaik, Ritto Kurian Babu, Purabi Mahato, "Parallel Prefix Adders- A Comparative Study For Fastest Response", Communication and Electronics Systems (ICCES), International Conference on IEEE 2016.

- [2] www.allaboutfpga.com.

- [3] G. Karthik Reddy,D. Sharat Babu Rao, "A Comparative study on Low-Power and High Speed Carry Select Adder", IEEE Sponsored 9th International Conference on Intelligent Systems and Control (ISCO)2015.

- [4] Mr. Deepak Raj, Mrs.Sahana K Adyanthaya, Prof. Praveen J, Prof. Raghavengra Rao R,"Design and Implementation of different types of efficient parallel prefix adders", INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERI NCAIET-2015.

- [5] Sudheer Kumar Yezerla, B Rajendra Naik, "Design and Estimation of delay, power and area for Parallel prefix adders", RAECS UIET Panjab University Chandigarh, 06 - 08 March, 2014.

- [6] Mr.Rajeswar Reddy B, Mr.Lakshmi Prasad E, Dr.A.R.Reddy, "Multi Precision Arithmetic Adders", INTERNATIONAL CONFERENCE ON COMPUTER COMMUNICATION AND INFORMATICS (ICCCI -2016), JAN. 07 – 09, COIMBATORE, INDIA 978-1-4673-6680-9/16/\$31.00 c 2016 IEEE.

- [7] Prof. Rashmi Rahul Kulkarni,"Comparison among Different Adders", IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 5, Issue 6, Ver. I (Nov -Dec. 2015).

- [8] Jasbir Kaur, Lalit Sood,"Comparison Between Various Types of Adder Topologies",IJCST Vol. 6, Iss ue 1, Jan -March 2015.