# Implementation of Fault Tolerant Filter Based on Error Correction Codes

Prof. D.S.Bhosale<sup>1</sup>, Fartale Pooja<sup>2</sup>, Bhosale Bharati<sup>3</sup>, Deokar Sayali<sup>4</sup>

<sup>1, 2, 3, 4</sup> Department of E&TC

<sup>1, 2, 3, 4</sup> BSIOTR College of Engineering and Research, Wagholi , Pun

Abstract- Digital filters are widely used in signal processing and communication systems. In some cases, the reliability of those systems is critical, and fault tolerant filter implementations are needed. Over the years, many techniques that exploit the filters' structure and properties to achieve fault tolerance have been proposed. As technology scales, it enables more complex systems that incorporate many filters.

In those complex systems, it is common that some of the filters operate in parallel, for example, by applying the same filter to different input signals.

Recently, a simple technique that exploits the presence of parallel filters to achieve fault tolerance has been presented. In this brief, that idea is generalized to show that parallel filters can be protected using error correction codes (ECCs) in which each filter is the equivalent of a bit in a traditional ECC. This new scheme allows more efficient protection when the number of parallel filters is large. The technique is evaluated using a case study of parallel finite impulse response filters showing the effectiveness in terms of protection and implementation cost.

Keywords- Error correction codes (ECCs), filters, soft errors.

## I. INTRODUCTION

Filters are often used in electronic systems to emphasize signals in certain frequency ranges and reject signals in other frequency ranges. In circuit theory, a filter is an electrical network that alters the amplitude and/or phase characteristics of a signal with respect to frequency. Ideally, a filter will not add new frequencies to the input signal, nor will it change the component frequencies of that signal, but it will change the relative amplitudes of the various frequency components and/or their phase relationships.

Today filters are widely used in number of applications which based on automotive, medical, and space where reliability of components in digital electronic circuits is critical. Filters of some sort are essential in the operation of most electronic circuits. There are many different bases of classifying filters and these overlap in many different ways; there is no simple hierarchical classification. As the behavioral properties of signal changes the techniques of filtering it will be differ. Being specific with filter, the digital filters have vast applications in digital signal processing. Filtering is also a class of signal processing, the defining feature of filters being the complete or partial suppression of some aspect of the signal. It is therefore in the interest of anyone involved in electronic circuit design to have the ability to develop filter circuits capable of meeting a given set of specifications. In signal processing, a digital filter is a device or process that removes some unwanted component or feature from a signal. Digital filters are used for two general purposes; separation of signals that have been combined, and restoration of signals that have been distorted in some way. Most often, this means removing some frequencies and not others in order to suppress interfering signals and reduce background noise.

## **II. LITERATURE SURVEY**

[1]In this paper, fault tolerance based system based on Error Correction Codes (ECCs) using VHDL is designed, implemented, and tested. It proposes that with the help of ECCs i.e. Error Correction Codes there will be more protected Parallel filter circuit has been possible. The filter they have used for error detection and correction are mainly finiteimulse response (FIR) filters. They have been used Hamming Codes for fault correction in which they takes a block of k bits and produces a block of n bits by adding n-k parity check bits. The parity check bits are XOR combinations of the k data bits. By properly designing those combinations it is possible to detect and correct errors. In this scheme they have used redundant module in which the data and parity check bits are stored and can be recovered later even if there is an error in one of the bits. This is done by re-computing the parity check bits and comparing the results with the values stored. In this way using hamming codes error can be detected and corrected within the circuit.

[2] In this paper, Triple Modular Redundancy (TMR) and Hamming Codes have been used to protect different circuits against Single Event Upsets (SEUs). In this paper, the use of a Novel Hamming approach on FIR Filters is studied and implemented in order to provide low complexity, reduce delay and area efficient protection techniques for higher bits data. A novel Hamming code is proposed in this paper, to increase the efficiency of higher data bits. In this paper, they have proposed technique used to demonstrate, how the lot of overhead due to interspersing the redundancy bits, their subsequent removal, pad to pad delay in the decoder and consumption of total area of FIR filter for higher bits are reduced. These are based on the novel hamming code implementation in the FIR filter instead of conventional hamming code used to protect FIR filter. In this scheme Hamming code used for transmission of 7-bit data item.

[3] In this paper, the design of a FIR filter with self checking capabilities based on the residue checking is analyzed. Usually the set of residues used to check the consistency of the results of the FIR filter are based of theoretic considerations about the dynamic range available with a chosen set of residues, the arithmetic characteristics of the errors caused by a fault and on the characteristic of the filter implementation. This analysis is often difficult to perform and to obtain acceptable fault coverage the set of chosen residues is overestimated. Obtained result and therefore requires that Instead, in this paper they have showed how using an exhaustive fault injection campaigns allows to efficiently select the best set of residues. Experimental results coming from fault injection campaigns on a 16 taps FIR filter demonstrated that by observing the occurred errors and the detection modules corresponding to different residue has been possible to reduce the number of detection module, while paying a small reduction of the percentage of SEUs that can be detected. Binary logic dominates the hardware implementation of DSP systems .

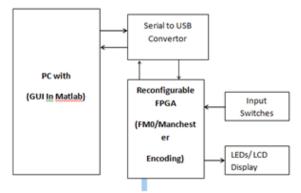

#### **Block Diagram-**

Fig. Block Diagram of System

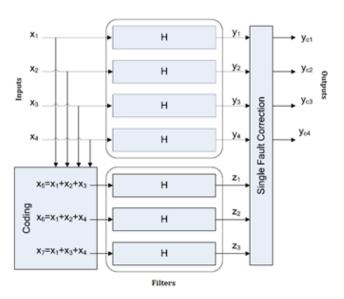

Fig. Architecture of Fault Tolerant Filer based Error Correcting Codes

#### ACKNOWLEDGMENT

We have pleasure in presenting this noble system. I express my honest and sincere thanks to our guide Prof. D. S. Bhosale for their consistent guidance, inspiration and sympathetic attitude throughout the seminar work.

We own sincere thanks, more than we can express, towards Dr. Y. S. Angal, Head of Department, E&TC, BSIOTR for his guidance, valuable suggestions and constant support throughout this work.

We are also thankful to all the staff members of Electronic & Telecommunication Department

We are highly obliged to Dr. T. K. Nagaraj, Principal, Bhivarabai Sawant Institute of Technology & Research, Wagholi, Pune. Who has been constant source of inspiration.

At last, we also like to thanks to our family. None of this would have been possible without the constant support and advice of our family.

### REFERENCES

"Fault Tolerant Parallel Filters Based on Error Correction Codes", Zhen Gao, Pedro Reviriego, Wen Pan, Zhan Xu, Ming Zhao, Jing Wang, and Juan Antonio Maestro.

- [2] "Area Efficient and Fault Tolerant FIR Filter", Brajesh Kumar Gupta (nit jamshedpur), Associate prof. R. Sinha ( nit jamshedpur )

- [3] "Fault-Tolerant Computation Within Complex FIR Filters.", P. Chan, G.A. Jullien, L. Imbert, V.S. Dimitrov, G.H. McGibney.

- [4] "Optimization of Self Checking FIR filters by means of Fault Injection Analysis", S. Pontarelli, L. Sterpone, G.C. Cardarilli, M. Re, M. Sonza Reorda, A. Salsano, M. Violante.

- [5] B. Shim and N. Shanbhag, "Energy-efficient soft errortolerant digital signal processing," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 4, pp. 336– 348, Apr. 2006.

- [6] R. W. Hamming, "Error correcting and error detecting codes," Bell Syst. Tech. J., vol. 29, pp. 147–160, Apr. 1950.

- [7] T. Hitana and A. K. Deb, "Bridging concurrent and nonconcurrent error detection in FIR filters," in Proc. Norchip Conf., 2004, pp. 75–78.

- [8] Y.-H. Huang, "High-efficiency soft-error-tolerant digital signal processing using fine-grain subword-detection processing," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 2, pp. 291–304, Feb. 2010.

- [9] S. Pontarelli, G. C. Cardarilli, M. Re, and A. Salsano, "Totally fault tolerant RNS based FIR filters," in Proc. IEEE IOLTS, Jul. 2008, pp. 192–194.

- [10] Z. Gao, W. Yang, X. Chen, M. Zhao, and J. Wang, "Fault missing rate analysis of the arithmetic residue codes based fault-tolerant FIR filter design," in Proc. IEEE IOLTS, Jun. 2012, pp. 130–133.

## AUTHORS

First Author –Pooja Fartale, BE E& TC, BSIOTR,Wagholi, poojafartale@gmail.com Second Author – Bhosale Bharati, BE E& TC, BSIOTR,Wagholi, bhosalebharati186@gmail.com Third Author – Deokar Sayali, BE E& TC, BSIOTR,Wagholi,poojafartale@gmail.com Correspondence Author – Bhosale Bharati, BE E& TC, BSIOTR,Wagholi, bhosalebharati186@gmail.com.(Mob.No.8888188712)