# Design High Speed Multiplier Using Vedic Mathematics For Iir Filter

Pratibha P. Dighe<sup>1</sup>, Aashish Mhaske<sup>2</sup>

<sup>1</sup>Dept of E&TC <sup>2</sup>Assistant Professor, Dept of E&TC <sup>1, 2</sup>DPCOE Pune, India

Abstract- Digital signal processing operation utilizing Vedic mathematics which performs the signal handling operation like convolution, circular convolution, cross correlation, autocorrelation and filter design. Digital signal processing (DSP) operations are vital part of engineering and medical field. Outlining of DSP operations have numerous methodologies. This configuration procedure gives the analysis of signals to enhance the accuracy of the mathematical calculations. It encourages the time sharing for all signals to process mathematical operations all the while. Vedic mathematics is the ancient math which has a unique method of mental calculation with the assistance of basic rules and standards based on sutras. The utilization of multiplier has demonstrated the efficiency of Urdhva-Tiryakbhayam method for multiplication which conveys a distinction in the real procedure of multiplication itself. The configuration of IIR filters utilizing Urdhva-Tiryakbhayam sutra. This calculation is performed in Xilinx and compare with MATLAB operation of IIR filter respectively.

*Keywords*- Vedic Mathematics, Multiplier, DSP, IIR Filter, Urdhwa Tiryagbhyam Sutra, MATLAB 8.1, Xilinx 14.5 ISE.

#### I. INTRODUCTION

Multipliers are basic building blocks of any processor design and normally we called as heart of DSPs. Modern multipliers speed of computation decreases as the inputs increase. There are many multipliers available today like Combinational multiplier, array multiplier, serial and parallel multiplier and many more. Thus building high speed multipliers for processor design is done using Vedic. In DSPs, Filtering is normally used and is applied to many applications like speech processing etc. Digital Signal Processing operations like convolution, Fast Fourier Transform, DFT calculation. Frequency sampling etc method is being used in many applications. Filtering is a method which is used for removing unwanted signal frequencies by being sensitive to the wanted signal frequencies. Digital audio or video when it is transmitted through the communication channel, noisy is added to the original signal. So, at receiver side filtering is must in order to get original one. Basically, filters are

Page | 1

Classified into 4 types depending upon the pass band and stop bands. FIR and IIR are two types of filter designed in this paper. Digital signal processing have to perform operations like frequency domain filtering (FIR, IIR) and frequency transformations like DFT, FFT, and DCT. For these operation multiplication is an essential hardware component. Thus the performance of the multiplier is a key element in determining the performance of the entire system. This isbecause the multiplier is the slowest and most time consuming element in the system. Thus the optimization of the multiplier speed and area is a major challenge for the system designers. This challenge can be successfully overcome by the use of ancient Vedic mathematics.

#### II. VEDIC MULTIPLIER

The use of Vedic mathematics is to reduces the typical calculations in conventional mathematics to very simple one. Because the Vedic formulae are claimed to be based on the natural principles on which the human mind works. Vedic Mathematics is a methodology of arithmetic rules that allow more efficient speed implementation. It also provides some effective algorithms which can be applied to various branches of engineering such as computing. A. Urdhva Tiryakbhyam Sutra The proposed Vedic multiplier is based on the "Urdhva Tiryagbhyam" sutra (algorithm). These Sutras have been traditionally used for the multiplication of two numbers in the decimal number system. In this work, we apply the same ideas to the binary number system to make the proposed algorithm compatible with the digital hardware. It is a general multiplication formula applicable to all cases of multiplication. It literally means "Vertically and Crosswise". It is based on a novel concept through which the generation of all partial products can be done with the concurrent addition of these partial products. The algorithm can be generalized for n x n bit number. Since the partial products and their sums are calculated in parallel and the multiplier is independent of the clock frequency of the processor. Due to its regular structure, it can be easily layout in microprocessors and designers can easily circumvent these problems to avoid catastrophic device failures. The processing power of multiplier can easily be increased by increasing the input and output data bus widths

since it has a quite a regular structure. Due to its regular structure, it can be easily layout in a silicon chip. The Multiplier based on this sutra has the advantage that as the number of bits increases, gate delay and area increases very slowly as compared to other conventional multipliers.

### III. URDHVA TIRYAKBHAYAM SUTRA FOR BINARY NUMBER SYSTEM

In this section this Sutra is extended to binary number system. To illustrate the multiplication algorithm, consider the multiplication of two binary numbers a3a2a1a0 and b3b2b1b0. As the result of this multiplication would be more than 4 bits, let it be as ...r3r2r1r0. Line diagram for multiplication of two 4-bit numbers is shown in Fig. 2 which is nothing but the mapping of the Fig. 1 in binary system. For the sake of simplicity, each bit is represented by a circle. Least significant bit r0 is obtained by multiplying the least significant bits of the multiplicand and the multiplier. The process is followed according to the steps shown in Fig. 2. As in the last case, the digits on the both sides of the line are multiplied and added with the carry from the previous step. This generates one of the bits of the result (rn) and a carry (say cn). This carry is added in the next step and hence the process goes on. If more than one line are there in one step, all the results are added to the previous carry. In each step, least significant bit acts as the result bit and the other entire bits act as carry. For example, if in some intermediate step, we get 110, then 0 will act as result bit and 11 as the carry (referred to as cn in this text). It should be clearly noted that can may be a multi-bit number. Thus the following expressions are coming:

| r0 = a0b0;                             | (1) |

|----------------------------------------|-----|

| c1r1 = a1b0 + a0b1;                    | (2) |

| c2r2 = c1 + a2b0 + a1b1 + a0b2;        | (3) |

| c3r3 = c2 + a3b0 + a2b1 + a1b2 + a0b3; | (4) |

| c4r4 = c3 + a3b1 + a2b2 + a1b3;        | (5) |

| c5r5 = c4 + a3b2 + a2b3;               | (6) |

| c6r6 = c5 + a3b3                       | (7) |

With c6r6r5r4r3r2r1r0 being the final product.

|   | STE | EP 1 |   |   | STE | <b>P</b> 2 |    |

|---|-----|------|---|---|-----|------------|----|

| 0 | 0   | 0    | 0 | 0 | 0   | 0/         | Vo |

| 0 | 0   | 0    | 0 | 0 | 0   | 0          | 0  |

|   | STE | EP 3 |   |   | STE | <b>P</b> 4 |    |

| 0 | 0   | 0+   | 0 | 0 | 0   | 0          | 0  |

| 0 | õ   | 0    | 0 | 0 | ó   | 0          | 0  |

|   | STE | EP 5 |   |   | STE | P 6        |    |

| 0 | 0   | 0    | 0 | 0 | 0   | 0          | 0  |

| 0 | 0   | 0    | 0 | 0 | 0   | 0          | 0  |

Line diagram for multiplication of two numbers

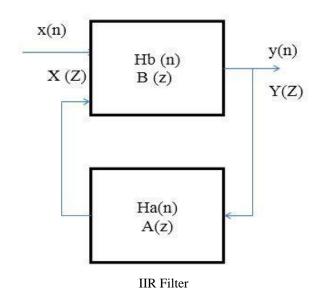

#### **IV. IIR FILTER**

IIR filters are digital filters with vast motivation reaction. Dissimilar to FIR filters, they have the feedback and are called recursive digital filters. IIR filters are digital filters with infinite impulse response. Unlike FIR filters, they have the feedback (a recursive part of a filter) and are known as recursive digital filters. Therefore for this reason IIR filters have much better frequency response than FIR filters of the same order. Unlike FIR filters, their phase characteristic is not linear which can cause a problem to the systems which need phase linearity. For this reason, it is not preferable to use IIR filters in digital signal processing when the phase is of the essence. Otherwise, when the linear phase characteristic is not important, the use of IIR filters is an excellent solution The IIR filters have vastly improved frequency reaction than FIR filters of the same request (order). Dissimilar to FIR filters, their stage trademark (phasecharacteristics) is not direct which can bring about an issue to the frameworks which need stage linearity. For this reason, it is not desirable over utilization IIR filters in digital signal when the phase is of the substance. FIR filters can have straight phase trademark that is certainly not of IIR filters. When it is important to have straight phase trademark, FIR filters are the main accessible arrangement. In different situations when straight phase trademark is redundant, for example, FIR filters, speech signal processing is bad arrangement. IIR filters ought to be utilized. The subsequent filter request is significantly lower for the same frequency reaction. The IIR filter transfer function is a proportion of two polynomials of complex variable z-1.The numerator characterize area of zeros, though the denominator characterizes area of poles of the subsequent IIR filter transfer function.

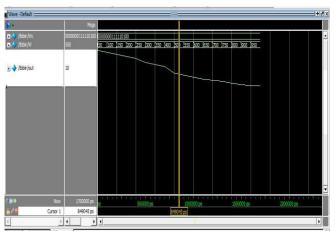

# PERFORMANCE ANALYSIS

Technology Schematic for 16X16 multiplier

Digital Output of 16X16 Multiplier

Analog Output of 16X16 Multiplier

| Table 1: 16x16 multiplier using | conventional multiplier           |

|---------------------------------|-----------------------------------|

| Number of slices:               | 525 out of 704<br>(74% utilized)  |

| Number of 4 input LUT's:        | 832 out of 1408 (65%<br>utilized) |

| Number of bonded IOB's:         | 105 out of 108                    |

(97% utilized)

Table 2: 16x16 multiplier using reversible gates

| Number of slices: | 510 out of 704 (72%<br>utilized) |

|-------------------|----------------------------------|

| Number of 4 input | 893 out of 704 (63%              |

| LUT's:            | utilized)                        |

| Number of bonded  | 65 out of 704 (60%               |

| IOB's:            | utilized)                        |

Table 3: Comparison of speed using various multipliers

| Technology used                            | Maximum Path Delay |

|--------------------------------------------|--------------------|

| 2x2 conventional<br>multiplier             | 7.167ns            |

| 2x2 multiplier using<br>reversible gates   | 7.167ns            |

| 4x4 conventional<br>multiplier             | 13.201 ns          |

| 4x4 multiplier using<br>reversible gates   | 12.972 ns          |

| 8x8 conventional<br>multiplier             | 26.177 ns          |

| 8x8 multiplier using<br>reversible gates   | 24.484 ns          |

| 16x16 conventional<br>multiplier           | 45.183ns           |

| 16x16 multiplier using<br>reversible gates | 40.21ns            |

The design and implementation of 16x16 multiplier uses the conventional multiplier which require more hardware (more no. gates), more delay. The table 1 and 2, 3 gives the summary of maximum path delay and no. of slices, LUT's and IOB's for both conventional multiplier and reversible gates which are used in proposed work. Tables shows that the efficiency of reversible gates is more than conventional multiplier as uses less no. of LUTs and IOB's, also makes the speed faster than conventional multiplier.

## **V. CONCLUSION**

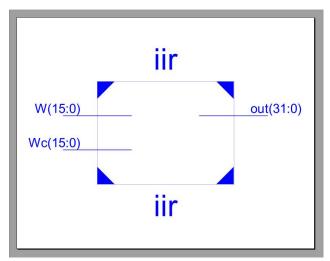

The proposed structure of IIR filters utilizing Urdhva Tiryagbhyam sutra of Vedic mathematics. This proposed design is performed in XILINX 14.5 ISE version. The sutras of Vedic mathematics are much more effective than customary mathematics. The Urdhva Tiryagbhyam sutra is faster than the customary method of multiplication. Thus IIR filter based on Vedic sutra taking less average processing time as compared to conventional methods

#### REFERENCES

- Tushar Shukla, Prabhat Kumar Shukla, Harish Prabhakar, "High Speed Multiplier for FIR Filter Design using Window", International Conference on Signal Processing and Integrated Networks (SPIN) IEEE 2014.

- [2] Sandesh S. Saokar, R.M. Banakar, Saroj Siddamal,

"High Speed Signed Multiplier for Digital Signal Processing Application"IEEE 2012.

- [3] Padma Kunthe, Sameena Zafar, Ankita Sharma, "16order IIR filter Design using Vedic Mathematics Technique", InternationalJournal of Engineering Innovation and Research. Volume 3, Issue 2 ISSN: 2277-5668. PP.No.138. 2014.

- [4] Padma Kunthe, Sameena Zafar, Ankita Sharma, "32-order IIR filter Design using Vedic mathematics", International Journal of Artificial Intelligence and Mechatronics. Volume 2, Issue 5, ISSN: 2320-5121. 2014.

- [5] Savita Srivastava, Dr. Deepak Nagaria "Design of High Performance FIR filter using Vedic Mathematics in MATLAB", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering. Vol.3, Issue 10, October2014.ISSN(print):2320-3765,

- [6] Pallavi Sathawane, D.V.Prasanthi, "An OptimalLow Power Adaptive Filter Design for NoiseReduction", International Journal ofScience,Engineering and Technology Research. Volume 3, Issue 9, September 2014.

- [7] Swapnil Manohar Mehkarkar, Snehal J.Banarase, "Implementation of High Speed FIR filter Based on AncientVedicMultiplicationTechnique", International Journal of emerging Technology and Advanced Engineering .volume 4, Issue5, May 2014. ISSN: 2250-2459.

- [8] Ms. Rajashri K. Bhongade, Ms. Sharada

G.Mungale,Mrs.KarunaBogawar,

"Implementation of Vedic Complex Multiplier for Digital

Signal Processing", International Journal Of engineering

Research and Applications (IJERA) ISSN: 2248-9622.

- [9] Mrs. Pooja, S. Puri, Mr. U.A. Patil, "High Speed Vedic Multiplier in FIR filter on FPGA", IOSR Journal of VLSI and signal Processing. Volume 4, Issue 3, ver.2(May-Jun.2014), PP 48-53, e-ISSN: 2319-4200, p-ISSN No.: 2319-4197.

- [10] P.saha, A.Banerji, A.dandupat, P.Bhattacharyya, "Vedic Mathematics Based 32-bit multiplicationDesignforHighSpeedLowPowerProcessors" ,International Journal on Smart Sensing and Intelligent Systems. Vol.4. No.2, June 2011.